基于e语言的验证自动化系统

验证技术的发展

在目前的集成电路设计中,芯片的规模和复杂程度正呈指数增加,为保证所设计芯片功能的正确性,需要花费比以往更多的时间和人力,困难度大幅增加。而且,目前的功能验证能力已经远远落后于设计能力,功能验证正成为大规模芯片设计的瓶颈。设计人员通常需要花费50%~70%的时间去验证他们的设计。虽然有形式验证等多种验证方法可供选择,但是设计者还是偏好基于仿真的验证,本文中的验证主要是指仿真。为了降低验证的工作量和提高验证的效率,越来越多的设计人员采用高级验证语言(HLV)来进行芯片验证。

验证技术的发展主要经历了以下几个阶段:

1. 基于HDL语言的验证

用HDL语言来建立测试平台和编写测试向量,将激励输入给设计,然后检查设计的输出。这种方法的缺点是测试平台和测试向量的建立和编写非常复杂和困难,并且验证所需的激励难以达到足够的覆盖率。

2. 面向对象的验证

由于采用HDL语言进行验证的局限性,设计人员可以使用面向对象的高级语言(如C++、Python)来建立验证环境和编写激励。这种验证方法可以使设计人员从比较抽象的设计高层,对设计的输入和输出进行建模,然后通过验证环境与仿真器的通信接口,将抽象的数据模型转换成比特形式的数据。这种验证方法大大降低了编写激励的工作量,但是验证环境的建立相对复杂,比如验证环境与仿真器的通信接口等。

3. 随机产生激励

由于测试激励编写的工作量非常大,所以设计人员逐步采用随机产生测试向量的方法,以减轻编写激励的工作量,并提高验证的覆盖率。但是它的缺点在于,由于激励是随机产生的,所以给验证结果的检查带来了一定难度,并且设计者不能根据要验证的设计属性来产生所需的激励,即不能根据约束来产生激励。

4. 验证平台工具

由于验证环境的建立过于复杂,因此出现了验证平台工具,通过这种工具可以大大减少建立验证环境的工作量。但是这类验证工具不能使验证人员通过设计的抽象层来编写激励,而且不能实现设计时序行为的检查。

验证自动化系统

由于上述验证方法都或多或少具有局限性,所以需要一种完善的验证系统。根据上节所述,一种完善的验证自动化系统需要具备以下几个功能:首先它能够定义验证计划;然后能够提供接口,用高级语言从抽象的层次产生基于约束的激励;并且能方便高效地建立验证环境;最后能够完成设计时序行为的验证和基于断言的功能覆盖率的验证。

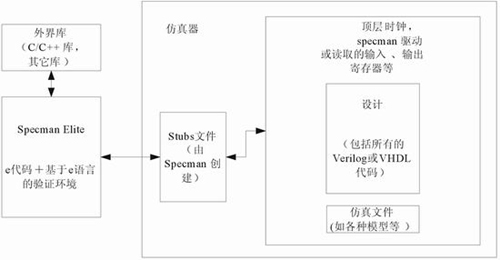

e语言是一种功能强大的验证语言,它可以很好地实现一个验证自动化系统,如图1所示。在这个验证系统中,首先可以根据验证者的需要,用e语言来制定一些约束,根据这些约束来产生验证需要的激励。由于e可以很好地与Verilog和VHDL仿真器通信,因此可以将这些用e语言抽象描述的数据转换成比特形式,然后加载给设计;再通过和仿真器的通信,对系统进行功能仿真,并将设计的输出收集起来,这时可以将比特形式的数据转换回e语言的抽象描述,以便于对设计行为与预期结果进行检查。除此之外,e语言还可以实现设计时序行为的检查。如果一个中断必须在请求后的5个周期后发出,可以通过e语言来描述这个设计属性,通过仿真来检查其是否满足。最后,e语言还可以用来进行基于断言的功能覆盖率验证。

基于e语言的验证环境与仿真器的交互

在具体介绍基于e语言的验证环境之前,先介绍一下基于e语言的验证环境与仿真器的通信机理。目前,Cadence公司的工具Specman Elite支持用e语言来建立验证自动化系统,Specman Elite提供可配置、可再使用和可扩展的验证组件,这些组件被称为eVC。eVC采用高级验证语言e编写,能够产生足够多的测试激励讯号,并能对设计行为与预期结果进行检查确认。eVC可以极大地缩短验证时间,提高产品品质。所以本文将以Specman为例来介绍基于e语言的验证环境与仿真器是如何协同工作的。

Specman和仿真器在仿真的过程中是两个独立并行的进程,它们通过通信接口(stubs文件)来进行通信,其结构如图2所示。

仿真环境包含以下各组成部分:

Specman:整个验证环境是用e语言实现的,其中包括约束、激励产生、驱动、检查、覆盖率等,所有的e文件都由Specman编译和仿真。

仿真器:Verilog或VHDL仿真器,它通过stubs文件与Specman进行通信。

外界库:仿真用到的一些模型可能是基于C语言的,e语言可以很好地导入这些模型来进行仿真。

设计:基于Verilog或VHDL的设计。

仿真文件:在仿真中可能用到的一些外部模型,如总线功能模型等。

顶层:包括设计和各种模型的例化和一些驱动输入或收集输出的寄存器。

Stubs文件:Specman读入所有的e文件,然后用一个命令来生成所需要的Stubs文件,这个文件在仿真过程中是由仿真器编译和仿真的。

基于e语言的验证环境

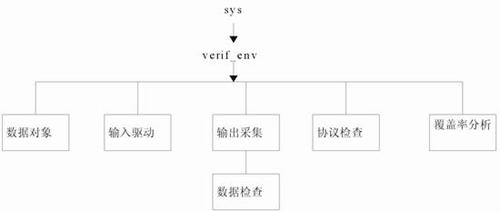

基于e语言的验证环境包括许多组成部分,其基本结构如图3所示。

其中数据对象代表固定格式的测试向量,如数据包、视频中的一帧数据,或CPU的一种指令。激励产生会对数据对象添加一定的约束,随机产生基于约束的激励。输入驱动中包括一个输入程序,负责将数据输入给设计,根据设计的不同,有可能对设计进行重复多次的输入。输出采集中包括一个采集设计输出的程序,并将采集到的数据转换成数据对象定义的形式,然后送到数据检查模块进行检查。数据检查部分产生所需要的数据和存储收集到的数据的程序,并完成数据检查。协议检查通过定义一些时序上的断言来监控设计的协议,如果违反了协议将产生警告或错误提示。覆盖率分析会分析设计中的断言,给出设计的功能覆盖率报告。

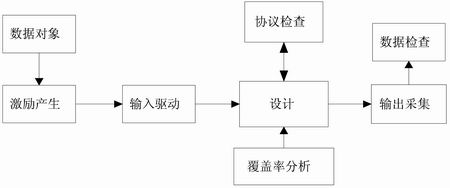

Specman提供约束解释器和通信信道来进行e语言的仿真,界面对象(interface object)负责将数据对象驱动给设计的界面,系统对象(system object)包括各种不同的界面对象。界面对象和系统对象根据每个设计来编写,如对CPU进行验证时,根据设计定义输入给CPU的数据对象(指令格式等),因此验证环境不需要随着设计的改变而改变,所以一个设计的环境是可以重用的。不同的测试激励通过约束数据对象、界面对象、系统对象来产生。验证环境的划分框图如图4所示。

基于e语言的验证环境的文件层次结构如图5所示,其最顶层文件名字固定为sys,在sys下例化所有的模块。

结语

本文介绍了目前国外各大芯片设计公司所采用的最新的验证技术——基于e语言的自动验证系统。采用e语言建立验证环境、编写测试激励,可大大降低芯片验证人员的工作量,提高验证效率。

录入时间:2007-10-05 来源:网络

相关文章:

• 射频EDA仿真软件介绍• 蓝牙HCI-UART与并口的FPGA控制接口设计

• 用EDA设计LED汉字滚动显示器

• 中、小尺寸TFT-LCD系统时序控制模块的设计

• 基于CPLD的多波形信号发生器设计

• 基于FPGA自适应数字频率计的设计

• 用CPLD实现单片机与ISA总线并行通信

• 电子系统EDA集成开发环境框架结构

• 基于多种EDA工具的FPGA设计

• FPGA系统的仿真和测试