基于CPLD的多波形信号发生器设计

在教学实验和教学研究中,信号发生器作为提供测试用电信号的仪器必不可少。目前通用的信号发生器一般只能输出常用的波形信号,不能满足某些特殊的需要,例如在电子测量教学中,通过用示波器测量晶体管的输出特性曲线实验,让学生理解晶体管测试仪的测量原理,就需要阶梯波信号。又如研究计数法测周期时,噪声信号引起的触发误差所需的某种噪声信号。鉴于教学实验和教学研究的需要,笔者设计了一种基于可编程逻辑器件CPLD的多波形信号发生器,此设计采用Max+Plus II开发平台,VHDL编程实现,整个系统除晶体振荡器和A/D转换外,全部集成在一片美国Altera公司生产的EPM7256SR208-15的芯片上。他除了输出常用的正弦波、三角波、方波以外,专门设计了一个任意波形模块(在本设计中为阶梯波波形数据),以及两种波形线性组合共10种波形。任意波形模块可由用户自行编辑所需波形数据,经下载在不改变整个系统硬件连接的情况下,输出用户所需的特殊波形。该信号发生器输出波形的频率可数控选择,其范围为100 Hz~30 kHz。幅度调节范围为0~5 V。

1 设计原理

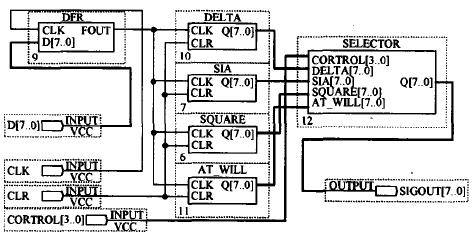

根据设计要求,多波形信号发生器由3部分组成,即时钟信号发生器、波形数据产生器和数/模转换电路。晶体振荡器产生稳定度很高的时钟信号,在时钟信号的作用下,波形数据产生器生成频率可变的波形数据数字信号,经数/模转换电路最终输出所需波形信号。幅度的调节可通过改变A/D转换芯片电阻网络的基准电压实现。基于CPLD的波形数据产生器顶层电路如图1所示。

图1 波形数据产生器顶层电路图

图中DFR为数控分频器,根据仪器面板8位数字量开关产生的预置数据D输出不同频率的时钟,以改变输出信号的频率。在时钟的作用下,DELTA,SIA,SQUARE,AT_WILL模块分别产生三角波、正弦波、方波和任意波形的波形数据。SELECTOR(数据选择器)在面板上的波形选择开关CORTROL的控制下,选择输出不同的波形数据,送至A/D转换电路。A/D转换采用8位的DAC0832芯片。

2 各模块电路设计

2.1 数控分频器设计

数控分频器的功能是在输入端输入不同数据时,对输入时钟产生不同的分频比,输出不同频率的时钟,以改变输出信号的频率。本设计中利用并行预置数的减法计数器实现,他的工作原理是:减法计数器在并行预置数的基础上,在时钟的作用下进行减计数,当计数值为零时产生溢出信号,加载预置数据,并且将溢出信号作为分频器的输出信号,实现N分频信号输出。其分频系数N为N = D+1。D为预置数的值。为了得到占空比为50%的矩形时钟信号,将输出再进行二分频。由此,该分频器的总分频系数为2N。本设计中一个波形周期由64个时钟信号组成,则输出信号频率为:

![]()

时钟频率为4 MHz。数控分频器如程序1。

[程序1]

--略去申明部分

entity dfr is

port(clk:in std_logic;d:in integer range 0 to 255;fout:out std_logic);

end dfr;

architecture one of dfr is

signal full:std_logic; //定义内部溢出标志信号

begin

process(clk)

variable cnt9:integer range 0 to 312;

//内部变量,位宽同预置数据端

begin

if clk'event and clk='1' then

if cnt9= 0 then cnt9:=d; //计数值为0时,产生溢出信号

full<='1'; //同时,同步加载预置数据d

else cnt9:=cnt9=1;full<='0';//否则,进行减1计数

end if;

end if;

end process;

--略去二分频进程

end one;

2.2 三角波波形数据产生模块设计

该模块可设计一个可逆计数器实现。设计时设置一变量作为工作状态标志,在此变量为全0时,当检测到时钟的上升沿时进行加同一个数操作,为全1时,进行减同一个数操作。由于A/D转换采用8位的DAC0832芯片,且设64个时钟为一个三角波周期,则输出Q每次加/减8。

2.3 正弦波波形数据产生模块设计

用加法计数器和译码电路完成。首先对幅度为1的正弦波的一个周期分为64个采样点,根据正弦波的函数关系计算得到每一点对应的幅度值,然后量化为8位二进制数据,最大值为255,最小值为0,以此得到正弦波波表。加法计数器生成译码电路的64个输入值,译码电路查波表输出。如程序2。

[程序2]

--略去申明和实体部分

architecture one of sia is

begin

process(clk,clr)

variable tmp:integer range 0 to 63;

begin

if clr='0' then q<=0;

elsif clk'event and clk='1' then

if tmp=63 then tmp:=0;

else tmp:=tmp+ 1;

end if;

case tmp is

--查表输出部分程序

when 00=> q<=0;when 01=> q<=1;when 02=> q<=4;

……

when 29=> q<=252;when 30=> q<= 254;when 31=> q<=255;

……

when 61=> q<=4;when 62=> q<=1 when 63=> q<=0;when others=> null;

end case;

end if;

end process;

end one;

2.4 方波波形数据产生模块设计

通过交替送出全0和全1,并给以32个时钟延时实现,64个时钟为一个周期。

2.5 任意波波形数据产生模块设计

设计原理同正弦波。译码器查表输出设计方法可以使用户编辑任意波形时,依据所需波表数据,修改CASE语句中条件赋值语句的赋值源数据即可。

2.6 数据选择器设计

用CASE语句设计完成。在CORTROL的控制下选择输出一种波形数据输出,同时完成两种波形的线性组合。波形组合是将波形每一时刻的数值相加,为了不超出DAC0832的输出范围,做相应的除2操作 。如程序3。

[程序3]

--略去申明和实体部分

architecture one of selector is begin

process(delta,sia,square,at_will,cortrol)

variable a:std_logic_vector(9 downto 0);

begin

case cortrol is

when "1000"=> q<= delta;when "0100"=> q<= sia;

when "0010"=> q<= square;when "0001"=> q<=at_will;

when "1100"=> a:="00"& delta+sia;q<=a(8 downto 1);

when "1010"=> a:="00"& delta+square;q<=a(8 downto 1);

when "1001"=> a:="00"& delta+at_will;q<= a (8 downto 1);

when "0110"=> a:="00"& sia+square;q<=a(8 downto 1);

when "0101"=> a:="00"& sia+at_will;q<=a(8 downto 1);

when "0011"=> a:="00"& square+at_will;q<=a(8 downto 1);

when others= > null:

end case;

end process;

end one;

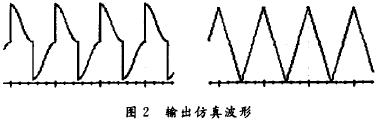

以上各模块电路在Max+Plus II开发平台上经编译、仿真符合设计要求后,用原理图输入法完成顶层电路的设计、综合,最后下载至型号为EPM7256SR208-15的CPLD芯片中,最终完成硬件电路连接。经测试符合设计要求。用Multisim仿真器仿真波形如图2所示。

图2中左图为正弦波+方波的输出波形,右图为三角波波形。从对输出10种波形的测试结果看:在整个频率范围内,频率误差最大为设计值的0.8%,最小为0.2%,低于传统的函数信号发生器的频率误差。

3 结语

实验表明,基于CPLD的多波形信号发生器实现了各种波形的产生,尤其是实现了传统的函数信号发生器不具有的一些波形的产生。输出波形频率按设计要求可调,并达到一定的精度。满足了教学实验和开发新的实验项目对特殊波形的要求。整个设计采用VHDL编程实现,其

设计过程简单,极易修改,可移植性强。另外由于CPLD具有可编程重置特性,因而可以方便地更换波形数据,且简单易行,所以为教学带来极大的方便。

录入时间:2007-09-28 来源:电子开发网 作者:郭海青

相关文章:

• 射频EDA仿真软件介绍• 蓝牙HCI-UART与并口的FPGA控制接口设计

• 用EDA设计LED汉字滚动显示器

• 中、小尺寸TFT-LCD系统时序控制模块的设计

• 基于CPLD的多波形信号发生器设计

• 基于FPGA自适应数字频率计的设计

• 用CPLD实现单片机与ISA总线并行通信

• 电子系统EDA集成开发环境框架结构

• 基于多种EDA工具的FPGA设计

• FPGA系统的仿真和测试