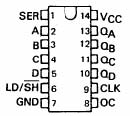

54LS295 / 74LS295 LSTTL型 4位双向通用移位寄存器(三态)

- 晶体管用肖特基二极管箝位

- 应用于: N位串—并转换器 N位并—串转换器

N位存储寄存器典型参数

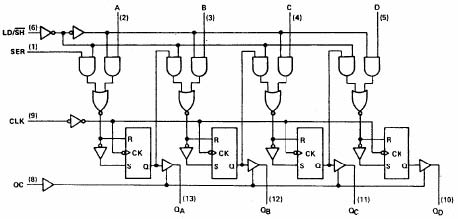

f工作频率=45MHz Pd=80mW(使能时)逻辑图

说明:

这种 4位寄存器采用并行输入、并行输出,并有时钟、串行、模式和输出控制输入。它有三种操作模式:并行(并排)寄存;右移(方向 QA到 QD);左移(方向 QD到 QA)。

并行寄存是通过四位数据并使模式控制输入为高电平来实现的。数据被存入相应的触发器,并在时钟输入从高变到低之后在输出端输出。在并行寄存期间,禁止送入串行数据。当模式控制输入为低时实现右移。当将每一个触发器的输出接前一触发器的输入(QD接输入 C等),使模式控制为高并在输入 D送入串行数据时,便实现左移。

当输出控制为高时,则四个输出端的标准逻辑电平可以驱动负载线或总线。如在输出控制输入端加一逻辑低电平,可由时钟电平独立地禁止这些输出。因此输出呈现高阻状态,既不能给总线加负载也不能驱动总线,但寄存器的操作时序并不受影响。

+:左移时,需将 QB外接 A,QC外接 B,QD外接 C,串行数据在输入 D端送入。 注:H=高电平(稳定态) L=低电平(稳定态) ×=不定(任何输入,包括转换)

↓=从高电平转换到低电平 a、b、|c、d=并行数据输入端 A、B、C、D的稳定态输入电平 QAO、QBO、QCO、QDO=在规定的稳定态输入条件建立之前 QA、QB、QC、QD的相应电平 QAn、QBn、QCn、QDn=在最近的时钟↓转换之前 QA、 QB、QC、QD的相应电平

推荐工作条件

| 符号 | 参数名称 | 74LS295 | 54LS295 | 单位 | ||||||

|---|---|---|---|---|---|---|---|---|---|---|

| 最小 | 典型 | 最大 | 最小 | 典型 | 最大 | |||||

| Vcc | 电源电压 | 4.75 | 5 | 5.25 | 4.5 | 5 | 5.5 | V | ||

| VIH | 输入高电平电压 | 2.0 | 2.0 | V | ||||||

| VIL | 输入低电平电压 | 0.8 | 0.7 | V | ||||||

| IOH | 输出高电平电流 | -2.6 | -1.0 | mA | ||||||

| IOL | 输出低电平电流 | 24 | 12 | mA | ||||||

| fCK | 时钟频率 | 0 | 30 | 0 | 30 | MHz | ||||

| tW | 时钟脉冲宽度 | 16 | 16 | ns | ||||||

| 建立时间(高电平或低电平数据) | 20 | 20 | ns | |||||||

| tsu | 建立时间 | 高电平 | 25 | 25 | ||||||

| (模式控制到时钟) | 低电平 | 30 | 30 | |||||||

| th | 保持时间(高电平或低电平) | 数据 | 20 | 20 | ns | |||||

| 模式控制到时钟 | 0 | 0 | ||||||||

| TA | 工作环境温度 | -40 | 85 | -55 | 125 | ℃ | ||||

电 性 能:(除特别说明外,均为全温度范围)

| 符号 | 参数名称 | 测试条件 | 74LS295 | 54LS295 | 单位 | |||||

|---|---|---|---|---|---|---|---|---|---|---|

| 最小 | 典型 | 最大 | 最小 | 典型 | 最大 | |||||

| VIK | 输入钳位电压 | Vcc=最小 II=-18mA | -1.5 | -1.5 | V | |||||

| VOH | 输出高电平电压 | Vcc=最小 VIL =最大 VIH=2V IOH =最大 | 2.4 | 2.4 | 3.1 | V | ||||

| VOL | 输出低电平电压 | Vcc=最小 VIL =最大 VIH=2V IOL =最大 | 0.5 | 0.25 | 0.4 | V | ||||

| IOZH | 高关态输出电流 | Vcc=最大 VIL=最大 Vo=2.7V | 20 | 20 | μA | |||||

| IOZL | 低关态输出电流 | Vcc=最大 VIH=2.0V Vo=0.4V | -20 | -20 | μA | |||||

| II | 输入电流 (最大输入电压时 ) | Vcc=最大 VI=7V | 0.1 | 0.1 | mA | |||||

| IIH | 输入高电平电流 | Vcc=最大 VI=2.7V | 20 | 20 | μA | |||||

| IIL | 输入低电平电流 | Vcc=最大 VI=0.4V | -0.4 | -0.4 | mA | |||||

| IOS | 输出短路电流 | Vcc=最大 VO=0V | -30 | -130 | -30 | -130 | mA | |||

| ICC | 电源电流 | Vcc=最大(注) | 条件 A | 29 | 20 | 29 | ||||

| 条件 B | 33 | 22 | 33 | mA | ||||||

注:在所有输出开路,数据输入接地,串行和模式控制输入接 4.5V情况下,Icc测量条

件如下: 条件A:输出控制 OC输入接4.5V,时钟输入先瞬时接高电平,然后接地; 条件B:输出控制和时钟输入接地。

所有典型值均在 Vcc=5.0V, T A=25℃下测量得出。 交流(开关)参数:Vcc=5.0V, TA=25℃

| 符号 | 参数名称 | 从(输入) | 到(输出) | 测试条件 | 参数值 | 单位 | |||

|---|---|---|---|---|---|---|---|---|---|

| 最小 | 典型 | 最大 | |||||||

| fmax | 最大时钟频率 | 时钟 CLK | 30 | 45 | MHz | ||||

| tPLH | 传输延迟时间 | 14 | 20 | ns | |||||

| tPHL | 传输延迟时间 | CL=45pF | 19 | 30 | ns | ||||

| tPZH | 输出使能时间 | 输出控制 | 任一输出 | 18 | 26 | ns | |||

| tPZL | 输出使能时间 | OC | RL=667Ω | 20 | 30 | ns | |||

| tPHZ | 输出禁止时间 | 输出控制 | CL=5 pF | 13 | 20 | ns | |||

| tPLZ | 输出禁止时间 | OC | RL=667Ω | 13 | 20 | ns | |||