# Functions from www.A-PDF.com to Compare the water look 160/3A

## CD54HCT160/3A

June 1997

### **Synchronous Presettable Counters**

#### Description

The CD54HC160/3A and CD54HCT160/3A devices are presettable synchronous counters that feature look-ahead carry logic for use in high-speed counting applications. The CD54HC160/3A and CD54HCT160/3A are asynchronous reset decade counters. Counting and parallel presetting are both accomplished synchronously with the negative-to-positive transition of the clock.

COMPLETE DATA SHEET **COMING SOON!**

A low level on the synchronous parallel enable input, SPE, disables the counting operation and allows data at the P0 to P3 inputs to be loaded into the counter (provided that the setup and hold requirements for SPE are met.)

All counters are reset with a low level on the Master Reset input,  $\overline{MR}$ .

Two count enables, PE and TE, in each counter are provided for n-bit cascading. In all counters, reset action occurs regardless of the level of the SPE, PE and TE inputs and the clock input, CP.

If a decade counter is preset to an illegal state or assumes an illegal state when power is applied, it will return to the normal sequence in one count.

The look-ahead carry features simplifiers serial cascading of the counters. Both count enable inputs (PE and TE) must be high to count. The TE input is gated with the Q outputs of all four stages so that at the maximum count the terminal count (TC) output goes high for one clock period. This TC pulse is used to enable the next cascaded stage.

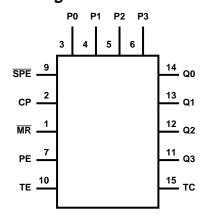

#### Functional Diagram

#### **HCT INPUT LOAD TABLE**

| INPUT   | UNIT LOAD (NOTE 1) |

|---------|--------------------|

| P0 - P3 | 0.25               |

| PE      | 0.65               |

| СР      | 1.05               |

| MR      | 0.8                |

| SPE     | 0.5                |

| TE      | 1.05               |

#### NOTE:

1. Unit load is  $\Delta I_{CC}$  limit specified in DC Electrical Specifications Table, e.g., 360μA Max at +25°C.

#### **Absolute Maximum Ratings**

| DC Supply Voltage, V <sub>CC</sub>                                                                | . 7.0)/   |

|---------------------------------------------------------------------------------------------------|-----------|

| Voltages Referenced to GND0.5V to                                                                 |           |

| DC Input Voltage Range, All Inputs, V <sub>IN</sub> 0.5V to V <sub>CC</sub>                       | ; +0.5V   |

| DC Output Voltage Range, All Outputs, V <sub>OUT</sub> 0.5V to V <sub>CO</sub>                    | +0.5V     |

| DC Input Diode Current, I <sub>IK</sub>                                                           |           |

| For $V_1 < -0.5V$ or $V_1 > V_{CC} + 0.5V$                                                        | ±20mA     |

| DC Output Diode Current, I <sub>OK</sub>                                                          |           |

| For $V_O < -0.5V$ or $V_O > V_{CC} + 0.5V$                                                        | ±20mA     |

| DC Drain Current, Per Output, I <sub>O</sub> , For -0.5V < V <sub>O</sub> < V <sub>CC</sub> + 0.5 | δV        |

| Standard Output                                                                                   | ±25mA     |

| Bus Driver Output                                                                                 |           |

| DC V <sub>CC</sub> or GND Current, I <sub>CC</sub>                                                |           |

| Standard Output                                                                                   | ±50mA     |

| Bus Driver Output                                                                                 |           |

| CALITION: Strasses above these listed in "Absolute Maximum Pating                                 | o" may aa |

| Power Dissipation Per Package, P <sub>D</sub>                 |

|---------------------------------------------------------------|

| $T_A = -55^{\circ}C$ to $+100^{\circ}C$ (Package F)           |

| $T_A = +100$ °C to $+125$ °C (Package F) Derate Linearly at   |

| 8mW/°C to 300mW                                               |

| Operating Temperature Range, T <sub>A</sub>                   |

| Package Type F55°C to +125°C                                  |

| Storage Temperature, T <sub>STG</sub> 65°C to +150°C          |

| Lead Temperature (During Soldering)                           |

| At Distance $1/16in. \pm 1/32in. (1.59mm \pm 0.79mm)$         |

| From Case For 10s Max                                         |

| Unit Inserted Into a PC Board (Min Thickness 1/16in., 1.59mm) |

| With Solder Contacting Lead Tips Only+300°C                   |

|                                                               |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### **Recommended Operating Conditions**

| Supply Voltage Range, V <sub>CC</sub>                                                | Operating Temperature Range, T <sub>A</sub> 55°C to +125°C |

|--------------------------------------------------------------------------------------|------------------------------------------------------------|

| T <sub>A</sub> = Full Package Temperature Range                                      | Input Rise and Fall Times, t <sub>R</sub> , t <sub>F</sub> |

| CD54HC Types                                                                         | at 2V                                                      |

| CD54HCT Types4.5V to 5.5V                                                            | at 4.5V                                                    |

| DC Input or Output Voltage, V <sub>IN</sub> , V <sub>OUT</sub> 0V to V <sub>CC</sub> | at 6V                                                      |