### DS1020 Programmable 8-Bit Silicon Delay Line

### www.dalsemi.com

#### **FEATURES**

- All-silicon time delay

- Models with 0.15 ns, 0.25 ns, 0.5 ns, 1 ns, and 2 ns steps

- Programmable using 3-wire serial port or 8-bit parallel port

- Leading and trailing edge accuracy

- Standard 16-pin DIP or 16-pin SOIC

- Economical

- Auto-insertable, low profile

- Low-power CMOS

- TTL/CMOS-compatible

- Vapor phase, IR and wave solderable

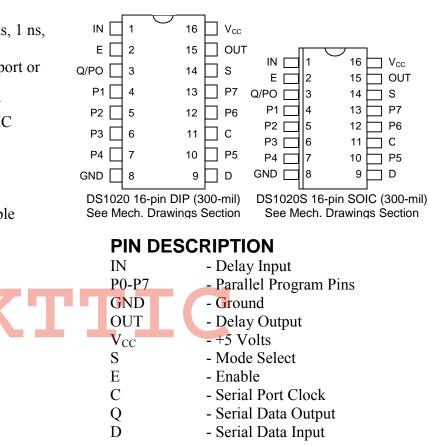

#### **PIN ASSIGNMENT**

#### DESCRIPTION

The DS1020 Programmable 8-Bit Silicon Delay Line consists of an 8-bit, user-programmable CMOS silicon integrated circuit. Delay values, programmed using either the 3-wire serial port or the 8-bit parallel port, can be varied over 256 equal steps. The fastest model (-15) offers a maximum delay of 48.25 ns with an incremental delay of 0.15 ns, while the slowest model (-200) has a maximum delay of 520 ns with an incremental delay of 2 ns. All models have an inherent (step-zero) delay of 10 ns. After the user-determined delay, the input logic state is reproduced at the output without inversion. The DS1020 is TTL- and CMOS-compatible, capable of driving 10 74LS-type loads, and features both rising and falling edge accuracy.

The all-CMOS DS1020 integrated circuit has been designed as a reliable, economic alternative to hybrid programmable delay lines. It is offered in a standard 16-pin auto-insertable DIP and a space-saving surface mount 16-pin SOIC.

### http://www.kttic.com

#### PARALLEL MODE (S=1)

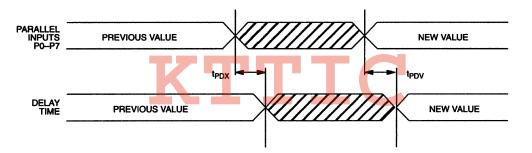

In the PARALLEL programming mode, the output of the DS1020 will reproduce the logic state of the input after a delay determined by the state of the eight program input pins P0 - P7. The parallel inputs can be programmed using DC levels or computer-generated data. For infrequent modification of the delay value, jumpers may be used to connect the input pins to  $V_{CC}$  and ground. For applications requiring frequent timing adjustment, DIP switches should be used. The enable pin (E) must be at a logic 1 in hardwired implementations.

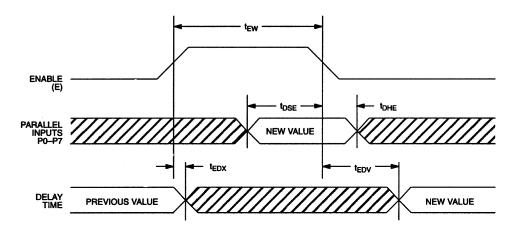

Maximum flexibility is obtained when the eight parallel programming bits are set using computergenerated data. When the data setup ( $t_{DSE}$ ) and data hold ( $t_{DHE}$ ) requirements are observed, the enable pin can be used to latch data supplied on an 8-bit bus. Enable must be held at a logic 1 if it is not used to latch the data. After each change in delay value, a settling time ( $t_{EDV}$  or  $t_{PDV}$ ) is required before input logic levels are accurately delayed.

Since the DS1020 is a CMOS design, unused input pins (D and C) must be connected to well-defined logic levels; they must not be allowed to float.

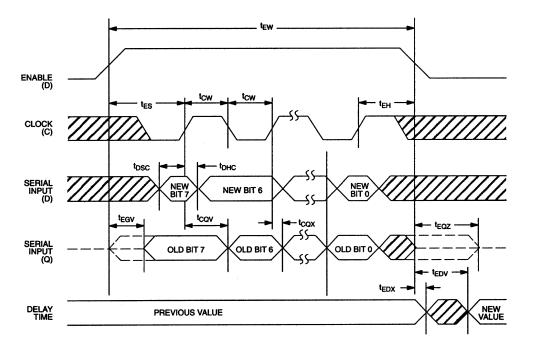

#### SERIAL MODE (S = 0)

In the SERIAL programming mode, the output of the DS1020 will reproduce the logic state of the input after a delay time determined by an 8-bit value clocked into serial port D. While observing data setup  $(t_{DSC})$  and data hold  $(t_{DHC})$  requirements, timing data is loaded in MSB-to-LSB order by the rising edge of the serial clock (C). The enable pin (E) must be at a logic 1 to load or read the internal 8-bit input register, during which time the delay is determined by the last value activated. Data transfer ends and the new delay value is activated when enable (E) returns to a logic 0. After each change, a settling time  $(t_{EDV})$  is required before the delay is accurate.

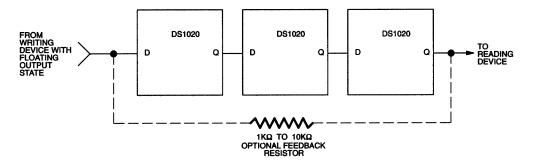

As timing values are shifted into the serial data input (D), the previous contents of the 8-bit input register are shifted out of the serial output pin (Q) in MSB-to-LSB order. By connecting the serial output of one DS1020 to the serial input of a second DS1020, multiple devices can be daisy-chained (cascaded) for programming purposes (Figure 3). The total number of serial bits must be eight times the number of units daisy-chained and each group of 8 bits must be sent in MSB-to-LSB order.

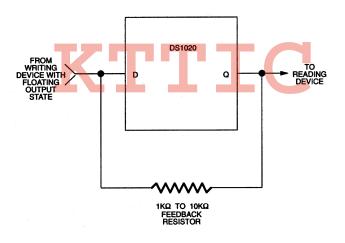

Applications can read the setting of the DS1020 delay line by connecting the serial output pin (Q) to the serial input (D) through a resistor with a value of 1k to 10k ohms (Figure 2). Since the read process is destructive, the resistor restores the value read and provides isolation when writing to the device. The resistor must connect the serial output (Q) of the last device to the serial input (D) of the first device of a daisy-chain (Figure 3). For serial readout with automatic restoration through a resistor, the device used to write serial data must go to a high impedance state.

To initiate a serial read, enable (E) is taken to a logic 1 while serial clock (C) is at a logic 0. After a waiting time ( $t_{EQV}$ ), bit 7 (MSB) appears on the serial output (Q). On the first rising (0  $\rightarrow$  1) transition of the serial clock (C), bit 7 (MSB) is rewritten and bit 6 appears on the output after a time  $t_{CQV}$ . To restore the input register to its original state, this clocking process must be repeated 8 times. In the case of a daisy-chain, the process must be repeated 8 times per package. If the value read is restored before enable (E) is returned to logic 0, no settling time ( $t_{EDV}$ ) is required and the programmed delay remains unchanged.

Since the DS1020 is a CMOS design, unused input pins (P1 - P7) must be connected to well-defined logic levels; they must not be allowed to float. Serial output Q/P0 should be allowed to float if unused.

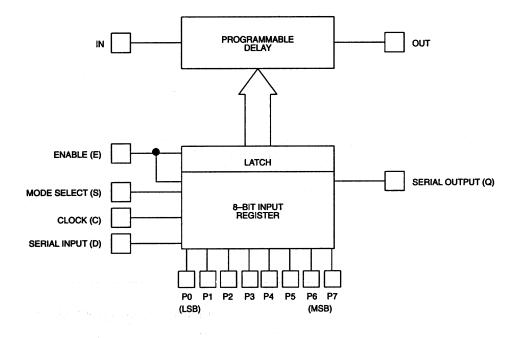

### FUNCTIONAL BLOCK DIAGRAM Figure 1

### SERIAL READOUT Figure 2

DS1020

#### PART NUMBER TABLE Table 1

|            | DELAYS AND TOLERANCES (IN ns) |            |                |                    |  |  |  |  |  |

|------------|-------------------------------|------------|----------------|--------------------|--|--|--|--|--|

| PART       | STEP ZERO                     | MAX DELAY  | DELAY CHANGE   | MAX DEVIATION FROM |  |  |  |  |  |

| NUMBER     | DELAY TIME                    | TIME (NOM) | PER STEP (NOM) | PROGRAMMED DELAY   |  |  |  |  |  |

| DS1020-15  | $10 \pm 2$                    | 48.25      | 0.15           | ±4                 |  |  |  |  |  |

| DS1020-25  | $10 \pm 2$                    | 73.75      | 0.25           | $\pm 6$            |  |  |  |  |  |

| DS1020-50  | $10 \pm 2$                    | 137.5      | 0.5            | $\pm 8$            |  |  |  |  |  |

| DS1020-100 | $10 \pm 2$                    | 265        | 1              | ±20                |  |  |  |  |  |

| DS1020-200 | $10 \pm 3$                    | 520        | 2              | $\pm 40$           |  |  |  |  |  |

#### **DELAYS VS. PROGRAMMED VALUE** Table 2

|                      | MIN<br>DELAY<br>STEP ZERO |         | K        | T       | т     | т     | J  |       |       | MAX<br>DELAY | PARALLEL<br>PORT | SERIAL<br>PORT |

|----------------------|---------------------------|---------|----------|---------|-------|-------|----|-------|-------|--------------|------------------|----------------|

| BINARY               | 0                         | 0       | 0        | 0       | 0     | 0     |    | 1     | 1     | 1            | P7               | MSB            |

| PROGRAMMED           | 0                         | 0       | 0        | 0       | 0     | 0     |    | 1     | 1     | 1            | P6               |                |

| VALUE                | 0                         | 0       | 0        | 0       | 0     | 0     |    | 1     | 1     | 1            | P5               |                |

|                      | 0                         | 0       | 0        | 0       | 0     | 0     |    | 1     | 1     | 1            | P4               |                |

|                      | 0                         | 0       | 0        | 0       | 0     | 0     |    | 1     | 1     | 1            | P3               |                |

|                      | 0                         | 0       | 0        | 0       | 1     | 1     |    | 1     | 1     | 1            | P2               |                |

| PART                 | 0                         | 0       | 1        | 1       | 0     | 0     |    | 0     | 1     | 1            | P1               |                |

| NUMBER               | 0                         | 1       | 0        | 1       | 0     | 1     |    | 1     | 0     | 1            | PO               | LSB            |

| DS1020-15            | 10.00                     | 10.15   | 10.30    | 10.45   | 10.60 | 10.75 |    | 47.95 | 48.10 | 48.25        |                  |                |

| DS1020-25            | 10.00                     | 10.25   | 10.50    | 10.75   | 11.00 | 11.25 |    | 73.25 | 73.50 | 73.75        |                  |                |

| DS1020-50            | 10.0                      | 10.5    | 11.0     | 11.5    | 12.0  | 12.5  |    | 136.5 | 137.0 | 137.5        |                  |                |

| DS1020-100           | 10                        | 11      | 12       | 13      | 14    | 15    |    | 263   | 264   | 265          |                  |                |

| DS1020-200           | 10                        | 12      | 14       | 16      | 18    | 20    | ſſ | 516   | 518   | 520          |                  |                |

| All delays in nanose | conde 1                   | afaranc | ed to in | nut nin |       |       | JJ |       |       |              |                  |                |

All delays in nanoseconds, referenced to input pin.

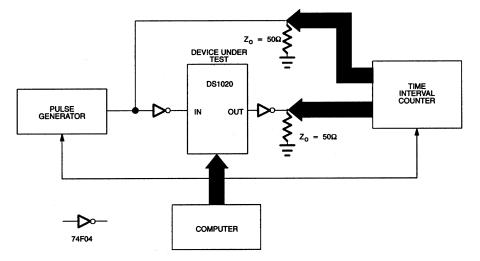

#### **TEST SETUP DESCRIPTION**

Figure 4 illustrates the hardware configuration used for measuring the timing parameters of the DS1020. The input waveform is produced by a precision pulse generator under software control. Time delays are measured by a time interval counter (20 ps resolution) connected to the output. The DS1020 serial and parallel ports are controlled by interfaces to a central computer. All measurements are fully automated with each instrument controlled by the computer over an IEEE 488 bus.

| <b>TEST CONDITIONS</b>             | S                            |              |                    |

|------------------------------------|------------------------------|--------------|--------------------|

| INPUT:                             | KT                           | ГТС          |                    |

| Ambient Temperature:               | $25^{\circ}C \pm 3^{\circ}C$ | Pulse Width: | 500 ns (DS1020–15) |

| Supply Voltage (V <sub>CC</sub> ): | $5.0V \pm 0.1V$              |              | 500 ns (DS1020–25) |

| Input Pulse:                       | $High = 3.0V \pm 0.1V$       |              | 2 µs (DS1020–50)   |

|                                    | $Low = 0.0V \pm 0.1V$        |              | 4 µs (DS1020–100)  |

| Source Impedance:                  | 50 ohms max.                 |              | 4 μs (DS1020–200)  |

| Rise and Fall Time:                | 3.0 ns max.                  | Period:      | 1 µs (DS1020–15)   |

|                                    | (measured between            |              | 1 μs (DS1020–25)   |

|                                    | 0.6V and 2.4V)               |              | 4 µs (DS1020–50)   |

|                                    |                              |              | 8 μs (DS1020–100)  |

|                                    |                              |              | 8 μs (DS1020-200)  |

NOTE: Above conditions are for test only and do not restrict the operation of the device under other data sheet conditions.

#### OUTPUT:

Output is loaded with a 74F04. Delay is measured between the 1.5V level of the rising edge of the input signal and the 1.5V level of the corresponding edge of the output.

5 of 9

#### **ABSOLUTE MAXIMUM RATINGS\***

Voltage on any Pin Relative to Ground Operating Temperature Storage Temperature Soldering Temperature Short Circuit Output Current -1.0V to +7.0V 0°C to 70°C -55°C to +125°C 260°C for 10 seconds 50 mA for 1 second

\* This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

| DC ELECTRICAL CHARACTERISTICS |                 |                        |      | $(0^{\circ}C \text{ to } 70^{\circ}C; V_{CC} = 5.0V \pm 5\%)$ |                      |       |       |  |  |

|-------------------------------|-----------------|------------------------|------|---------------------------------------------------------------|----------------------|-------|-------|--|--|

| PARAMETER                     | SYM             | TEST                   | MIN  | ТҮР                                                           | MAX                  | UNITS | NOTES |  |  |

|                               |                 | CONDITION              |      |                                                               |                      |       |       |  |  |

| Supply Voltage                | V <sub>CC</sub> |                        | 4.75 | 5.00                                                          | 5.25                 | V     | 1     |  |  |

| High Level                    | V <sub>IH</sub> |                        | 2.2  |                                                               | V <sub>CC</sub> +0.5 | V     | 1     |  |  |

| Input Voltage                 |                 |                        |      |                                                               |                      |       |       |  |  |

| Low Level                     | V <sub>IL</sub> |                        | -0.5 |                                                               | 0.8                  | V     | 1     |  |  |

| Input Voltage                 |                 |                        |      |                                                               |                      |       |       |  |  |

| Input Leakage                 | I <sub>1</sub>  | $0 \le V_I \le V_{CC}$ | -1.0 |                                                               | 1.0                  | μA    |       |  |  |

| Current                       |                 |                        |      |                                                               |                      |       |       |  |  |

| Active Current                | I <sub>CC</sub> | V <sub>CC</sub> =MAX;  |      |                                                               | 30.0                 | mA    | 3     |  |  |

|                               |                 | PERIOD=1 µs            |      |                                                               |                      |       |       |  |  |

| High Level                    | I <sub>OH</sub> | V <sub>CC</sub> =MIN.  |      |                                                               | -1.0                 | mA    |       |  |  |

| Output Current                |                 | V <sub>OH</sub> =2.7V  |      |                                                               |                      |       |       |  |  |

| Low Level                     | I <sub>OL</sub> | V <sub>CC</sub> =MIN.  | 8    |                                                               |                      | mA    | 4     |  |  |

| Output Current                |                 | $V_{OL}=0.5V$          |      |                                                               |                      |       |       |  |  |

| AC ELECTRICAL C        | STICS            | $(0^{\circ}C \text{ to } 70^{\circ}C; V_{CC} = 5V \pm 5\%)$ |     |     |       |       |

|------------------------|------------------|-------------------------------------------------------------|-----|-----|-------|-------|

| PARAMETER              | SYMBOL           | MIN                                                         | ТҮР | MAX | UNITS | NOTES |

| Clock Frequency        | $f_{\rm C}$      |                                                             |     | 10  | MHz   |       |

| Enable Width           | $t_{\rm EW}$     | 50                                                          |     |     | ns    |       |

| Clock Width            | $t_{\rm CW}$     | 50                                                          |     |     | ns    |       |

| Data Setup to Clock    | t <sub>DSC</sub> | 30                                                          |     |     | ns    |       |

| Data Hold from Clock   | t <sub>DHC</sub> | 10                                                          |     |     | ns    |       |

| Data Setup to Enable   | t <sub>DSE</sub> | 30                                                          |     |     | ns    |       |

| Data Hold from Enable  | t <sub>DHE</sub> | 20                                                          |     |     | ns    |       |

| Enable to Serial       | t <sub>EQV</sub> |                                                             |     | 50  | ns    |       |

| Output Valid           |                  |                                                             |     |     |       |       |

| Enable to Serial       | t <sub>EQZ</sub> | 0                                                           |     | 50  | ns    |       |

| Output High Z          |                  |                                                             |     |     |       |       |

| Clock to Serial        | t <sub>CQV</sub> |                                                             |     | 50  | ns    |       |

| Output Valid           |                  |                                                             |     |     |       |       |

| Clock to Serial        | t <sub>CQX</sub> | 10                                                          |     |     | ns    |       |

| Output Invalid         |                  |                                                             |     |     |       |       |

| Enable Setup to Clock  | t <sub>ES</sub>  | 50                                                          |     |     | ns    |       |

| Enable Hold from Clock | t <sub>EH</sub>  | 50                                                          |     |     | ns    |       |

| Parallel Input Valid   | t <sub>PDV</sub> |                                                             |     | 50  | μs    |       |

| to Delay Valid         |                  |                                                             |     |     |       |       |

| (cont'd)                        |                                     |                      |         |     |       |       |

|---------------------------------|-------------------------------------|----------------------|---------|-----|-------|-------|

| PARAMETER                       | SYMBOL                              | MIN                  | TYP     | MAX | UNITS | NOTES |

| Parallel Input Change           | t <sub>PDX</sub>                    | 0                    |         |     | ns    |       |

| to Delay Invalid                |                                     |                      |         |     |       |       |

| Enable to Delay Valid           | $t_{\rm EDV}$                       |                      |         | 50  | μs    |       |

| Enable to Delay Invalid         | $t_{EDX}$                           | 0                    |         |     | ns    |       |

| V <sub>CC</sub> Valid to Device | t <sub>PU</sub>                     |                      |         | 100 | ms    |       |

| Functional                      |                                     |                      |         |     |       |       |

| Input Pulse Width               | t <sub>WI</sub>                     | 100% of Output       |         |     | ns    |       |

|                                 |                                     | Delay                |         |     |       |       |

| Input to Output Delay           | t <sub>PLH</sub> , t <sub>PHL</sub> |                      | Table 2 |     | ns    | 2     |

| Input Period                    | Period                              | 2 (t <sub>WI</sub> ) |         |     | ns    |       |

| CAPACITANCE       |                 |     |     |     |       | $(I_A = 25^{\circ}C)$ |  |  |

|-------------------|-----------------|-----|-----|-----|-------|-----------------------|--|--|

| PARAMETER         | SYMBOL          | MIN | TYP | MAX | UNITS | NOTES                 |  |  |

| Input Capacitance | C <sub>IN</sub> |     |     | 10  | pF    |                       |  |  |

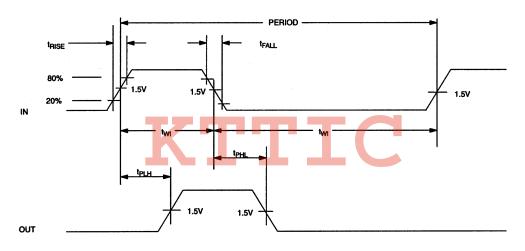

### TIMING DIAGRAM: SILICON DELAY LINE Figure 5

### TERMINOLOGY

**Period:** The time elapsed between the leading edge of the first pulse and the leading edge of the following pulse.

$t_{WI}$  (Pulse Width): The elapsed time on the pulse between the 1.5V point on the leading edge and the 1.5V point on the trailing edge, or the 1.5V point on the trailing edge and the 1.5V point on the leading edge.

$t_{RISE}$  (Input Rise Time): The elapsed time between the 20% and the 80% point on the leading edge of the input pulse.

$t_{FALL}$  (Input Fall Time): The elapsed time between the 80% and the 20% point on the trailing edge of the input pulse.

$t_{PLH}$  (Time Delay, Rising): The elapsed time between the 1.5V point on the leading edge of the input pulse and the 1.5V point on the leading edge of the output pulse.

$t_{PHL}$  (Time Delay, Falling): The elapsed time between the 1.5V point on the trailing edge of the input pulse and the 1.5V point on the trailing edge of the output pulse.

#### TIMING DIAGRAM: NON-LATCHED PARALLEL MODE (S = 1, E = 1) Figure 6

#### TIMING DIAGRAM: LATCHED PARALLEL MODE (S=1) Figure 7

http://www.kttic.com

### TIMING DIAGRAM: SERIAL MODE (S = 0) Figure 8

#### NOTES:

- 1. All voltages are referenced to ground.

- 2.  $@V_{CC} = 5V$  and 25°C. Delay accurate on both rising and falling edges within tolerances given in Table 1.

- 3. Measured with output open.

- 4. The "Q" output will only source 4 mA. This pin is only intended to drive other DS1020s.