http://www.kttic.com MITSUBISHI SEMICONDUCTOR < Dual-In-Line Package Intelligent Power Module>

## PS21563-P

TRANSFER-MOLD TYPE INSULATED TYPE

#### PS21563-P

#### INTEGRATED POWER FUNCTIONS

600V/10A low-loss  $5^{th}$  generation inverter bridge for three phase DC-to-AC power conversion

#### INTEGRATED DRIVE, PROTECTION AND SYSTEM CONTROL FUNCTIONS

- For upper-leg IGBTs :Drive circuit, High voltage isolated high-speed level shifting, Control supply under-voltage (UV) protection.

- For lower-leg IGBTs: Drive circuit, Control supply under-voltage protection (UV), Short circuit protection (SC).

- Fault signaling: Corresponding to an SC fault (Lower-leg IGBT) or a UV fault (Lower-side supply).

- Input interface: 3, 5V line CMOS/TTL compatible. (High Active)

- UL Approved : Yellow Card No. E80276

## **APPLICATION**

AC100V~200V inverter drive for small power motor control.

# KTTIC http://www.kttic.com MITSUBISHI SEMICONDUCTOR <Dual-In-Line Package Intelligent Power Module>

## PS21563-P

TRANSFER-MOLD TYPE **INSULATED TYPE**

## MAXIMUM RATINGS (Tj = 25°C, unless otherwise noted)

#### **INVERTER PART**

| Symbol     | Parameter                          | Condition                | Ratings  | Unit |

|------------|------------------------------------|--------------------------|----------|------|

| Vcc        | Supply voltage                     | Applied between P-N      | 450      | V    |

| VCC(surge) | Supply voltage (surge)             | Applied between P-N      | 500      | V    |

| VCES       | Collector-emitter voltage          |                          | 600      | V    |

| ±lc        | Each IGBT collector current        | Tf = 25°C                | 10       | Α    |

| ±ICP       | Each IGBT collector current (peak) | Tf = 25°C, less than 1ms | 20       | Α    |

| Pc         | Collector dissipation              | Tf = 25°C, per 1 chip    | 20       | W    |

| Tj         | Junction temperature               | (Note 1)                 | -20~+125 | °C   |

Note 1 : The maximum junction temperature rating of the power chips integrated within the DIP-IPM is  $150^{\circ}$ C (@ Tf  $\leq 100^{\circ}$ C) however, to ensure safe operation of the DIP-IPM, the average junction temperature should be limited to Tj(ave)  $\leq 125^{\circ}$ C (@ Tf  $\leq 100^{\circ}$ C).

#### **CONTROL (PROTECTION) PART**

| Symbol | Parameter                     | Condition                                       | Ratings     | Unit |

|--------|-------------------------------|-------------------------------------------------|-------------|------|

| VD     | Control supply voltage        | Applied between VP1-VNC, VN1-VNC                | 20          | V    |

| VDB    | Control supply voltage        | Applied between Vufb-Vufs, Vvfb-Vvfs, Vwfb-Vwfs | 20          | ٧    |

| VIN    | Input voltage                 | Applied between UP, VP, WP, UN, VN, WN-VNC      | -0.5~VD+0.5 | ٧    |

| VFO    | Fault output supply voltage   | Applied between Fo-VNC                          | -0.5~VD+0.5 | V    |

| IFO    | Fault output current          | Sink current at Fo terminal                     | 1           | mA   |

| Vsc    | Current sensing input voltage | Applied between CIN-VNC                         | -0.5~VD+0.5 | ٧    |

#### **TOTAL SYSTEM**

| Symbol    | Parameter                                                                  | Condition                                                                    | Ratings          | Unit |

|-----------|----------------------------------------------------------------------------|------------------------------------------------------------------------------|------------------|------|

| VCC(PROT) | Self protection supply voltage limit (short circuit protection capability) | VD = 13.5~16.5V, Inverter part<br>Tj = 125°C, non-repetitive, less than 2 μs | 400              | V    |

| Tf        | Module case operation temperature                                          | (Note 2)                                                                     | <b>−</b> 20~+100 | °C   |

| Tstg      | Storage temperature                                                        |                                                                              | <b>−</b> 40~+125 | °C   |

| Viso      | Isolation voltage                                                          | 60Hz, Sinusoidal, 1 minute,<br>All connected pins to heat-sink plate         | 2500             | Vrms |

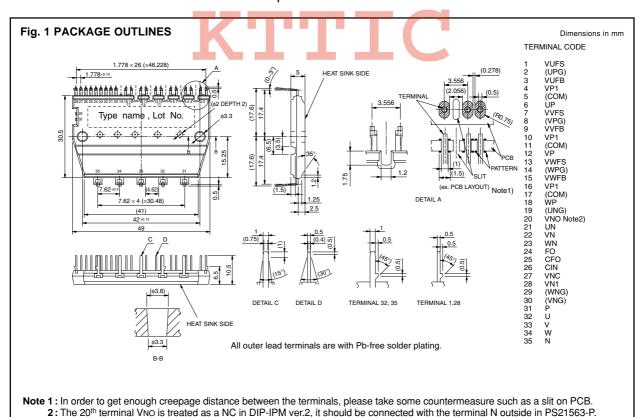

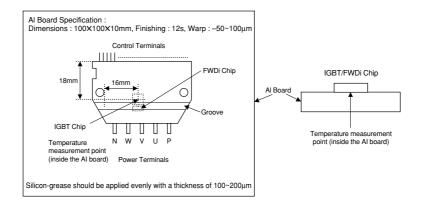

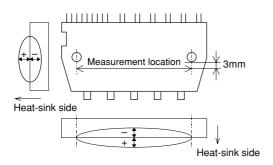

Note 2: Tf measurement point

TRANSFER-MOLD TYPE **INSULATED TYPE**

#### THERMAL RESISTANCE

| Cumphal          | Davamatav                | Condition                           | Limits |      |      | Unit |

|------------------|--------------------------|-------------------------------------|--------|------|------|------|

| Symbol Parameter |                          | Condition                           |        | Тур. | Max. |      |

| Rth(j-f)Q        | Junction to case thermal | Inverter IGBT part (per 1/6 module) | _      | _    | 5.0  | °C/W |

| Rth(j-f)F        | resistance (Note 3)      | Inverter FWD part (per 1/6 module)  | _      | _    | 6.5  | °C/W |

Note 3: Grease with good thermal conductivity should be applied evenly with about +100µm~+200µm on the contacting surface of DIP-IPM and heat-sink.

## **ELECTRICAL CHARACTERISTICS** (Tj = 25°C, unless otherwise noted)

#### **INVERTER PART**

| Cumphal                      | Davasatas                 | Condition                                                                        |                      | Limits |      |      | Unit  |  |

|------------------------------|---------------------------|----------------------------------------------------------------------------------|----------------------|--------|------|------|-------|--|

| Symbol                       | Parameter                 |                                                                                  |                      | Min.   | Тур. | Max. | Unit  |  |

| Collector-emitter saturation |                           | VD = VDB = 15V                                                                   | Ic = 10A, Tj = 25°C  | _      | 1.60 | 2.10 |       |  |

| VCE(sat)                     | voltage                   | VIN = 5V                                                                         | Ic = 10A, Tj = 125°C | _      | 1.70 | 2.20 | \ \ \ |  |

| VEC                          | FWD forward voltage       | Tj = 25°C, -IC = 10A, VIN = 0V                                                   |                      | _      | 1.50 | 2.00 | V     |  |

| ton                          |                           |                                                                                  | 0.60                 | 1.20   | 1.80 | μs   |       |  |

| trr                          |                           | VCC = 300V, VD = VDB = 15V<br>IC = 10A, Tj = 125°C, VIN = $0 \leftrightarrow 5V$ |                      | _      | 0.30 | _    | μs    |  |

| tc(on)                       | Switching times           |                                                                                  |                      | _      | 0.40 | 0.60 | μs    |  |

| toff                         |                           | Inductive load (upper-lo                                                         | wer arm)             | _      | 1.40 | 2.10 | μs    |  |

| tc(off)                      |                           |                                                                                  |                      | _      | 0.50 | 0.80 | μs    |  |

| ICES                         | Collector-emitter cut-off | Voc. Voc.                                                                        | Tj = 25°C            | _      | _    | 1    | mA    |  |

|                              | current VCE = VCES        |                                                                                  | Tj = 125°C           | _      | _    | 10   | IIIA  |  |

#### **CONTROL (PROTECTION) PART**

| Symbol   | Parameter                    |                                                     | Condition                                      |           | Limits |      |       | Unit |

|----------|------------------------------|-----------------------------------------------------|------------------------------------------------|-----------|--------|------|-------|------|

| Symbol   | i arameter                   | Condition                                           |                                                | Min.      | Тур.   | Max. | Offic |      |

|          |                              | VD = VDB = 15V                                      | Total of VP1-VNC, VN1-V                        | NC        | _      | _    | 5.00  |      |

| lD       | Circuit current              | VIN = 5V                                            | Vufb-Vufs, Vvfb-Vvfs,                          | Vwfb-Vwfs | _      | _    | 0.40  | mA   |

|          | Circuit current              | VD = VDB = 15V                                      | Total of VP1-VNC, VN1-VI                       | NC        | _      | _    | 7.00  | IIIA |

|          |                              | VIN = 0V                                            | VUFB-VUFS, VVFB-VVFS,                          | Vwfb-Vwfs | _      | _    | 0.55  |      |

| VFOH     | Fault output voltage         | Vsc = 0V, Fo circuit pull-up to 5V with $10k\Omega$ |                                                | 4.9       | _      | _    | V     |      |

| VFOL     | Fault output voltage         | VSC = 1V, IFO = 1mA                                 |                                                | _         | _      | 0.95 | V     |      |

| VSC(ref) | Short circuit trip level     | $T_f = -20 \sim 100 \circ C, V_D = 15V$ (Note 4)    |                                                | 0.45      | _      | 0.52 | V     |      |

| lin      | Input current                | VIN = 5V                                            |                                                |           | 1.0    | 1.5  | 2.0   | mA   |

| UVDBt    |                              |                                                     | Trip level                                     |           | 10.0   | _    | 12.0  | V    |

| UVDBr    | Control supply under-voltage | T <sub>i</sub> ≤ 125°C                              | Reset level                                    |           | 10.5   | _    | 12.5  | V    |

| UVDt     | protection                   | 1] \( \) 125 C                                      | Trip level                                     |           | 10.3   | _    | 12.5  | V    |

| UVDr     |                              |                                                     | Reset level                                    |           | 10.8   | _    | 13.0  | V    |

| tFO      | Fault output pulse width     | CFO = 22nF (Note 5)                                 |                                                | 1.0       | 1.8    | _    | ms    |      |

| Vth(on)  | ON threshold voltage         | Applied between LID VID WID VAID LINE VALVAGE       |                                                | 2.1       | 2.3    | 2.6  | V     |      |

| Vth(off) | OFF threshold voltage        | Abblied permeeti C                                  | Applied between UP, VP, WP-Vnc, Un, Vn, Wn-Vnc |           | 0.8    | 1.4  | 2.1   | V    |

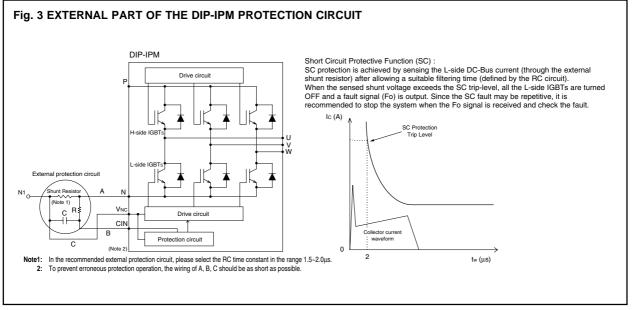

Note 4: Short circuit protection is functioning only for the lower-arms. Please select the external shunt resistance such that the SC trip-level is less than 2.0 times of the current rating.

<sup>5:</sup> Fault signal is asserted corresponding to a short circuit or lower side control supply under-voltage failure. The fault output pulse width tFO depends on the capacitance value of CFO according to the following approximate equation: CFO = 12.2 × 10<sup>-6</sup> × tFO [F].

TRANSFER-MOLD TYPE **INSULATED TYPE**

#### **MECHANICAL CHARACTERISTICS AND RATINGS**

| Davamatar          | Condition           |                        | Limits |      |      | Unit |

|--------------------|---------------------|------------------------|--------|------|------|------|

| Parameter          | Col                 | Min.                   | Тур.   | Max. | Unit |      |

| Mounting torque    | Mounting screw : M3 | Recommended : 0.78 N·m | 0.59   | _    | 0.98 | N·m  |

| Weight             |                     |                        | _      | 20   | _    | g    |

| Heat-sink flatness | (Note 6)            |                        | -50    | _    | 100  | μm   |

Note 6: Measurement point of heat-sink flatness

#### RECOMMENDED OPERATION CONDITIONS

| 0                           | Davarantan                          | O su distant                                                                           |                                                      | Reco | mmended | value | 1.1  |

|-----------------------------|-------------------------------------|----------------------------------------------------------------------------------------|------------------------------------------------------|------|---------|-------|------|

| Symbol                      | Parameter                           | Condition                                                                              | Min.                                                 | Тур. | Max.    | Unit  |      |

| Vcc                         | Supply voltage                      | Applied between P-N                                                                    |                                                      | 0    | 300     | 400   | V    |

| VD                          | Control supply voltage              | Applied between VP1-VNC, VN1-VN                                                        | С                                                    | 13.5 | 15.0    | 16.5  | V    |

| VDB                         | Control supply voltage              | Applied between VUFB-VUFS, VVFB                                                        | -Vvfs, Vwfb-Vwfs                                     | 13.0 | 15.0    | 18.5  | V    |

| $\Delta V$ D, $\Delta V$ DB | Control supply variation            |                                                                                        |                                                      | -1   | _       | 1     | V/µs |

| tdead                       | Arm shoot-through blocking time     | For each input signal, Tf ≤ 100°C                                                      |                                                      | 1.5  | _       | _     | μs   |

| fPWM                        | PWM input frequency                 | Tf ≤ 100°C, Tj ≤ 125°C                                                                 |                                                      | _    | _       | 20    | kHz  |

| lo A                        | Allowable r.m.s. current            | VCC = 300V, VD = VDB = 15V,                                                            | fPWM = 5kHz                                          | _    | _       | 6.5   |      |

|                             |                                     | P.F = 0.8, sinusoidal output<br>$Tf \le 100^{\circ}C$ , $Tj \le 125^{\circ}C$ (Note 7) | fPWM = 15kHz                                         | _    | _       | 4.0   | Arms |

| PWIN(on)                    |                                     |                                                                                        | (Note 8)                                             | 0.3  | _       | _     |      |

|                             |                                     | 200 ≤ Vcc ≤ 350V,<br>13.5 ≤ VD ≤ 16.5V,                                                | Below rated current                                  | 0.5  | _       | _     |      |

| PWIN(off)                   | Allowable minimum input pulse width | 13.0 ≤ VDB ≤ 18.5V,<br>-20°C ≤ Tf ≤ 100°C,                                             | Between rated current and 1.7 times of rated current | 0.5  | _       | _     | μs   |

|                             |                                     | N-line wiring inductance less than 10nH (Note 9)                                       | Between 1.7 times and 2.0 times of rated current     | 0.7  | _       | _     |      |

| Vnc                         | VNC variation                       | Between VNC-N (including surge)                                                        |                                                      | -5.0 | _       | 5.0   | V    |

- Note 7: The allowable r.m.s. current value depends on the actual application conditions.

8: The input pulse width less than PWIN(on) might make no response.

9: IPM might not work properly or make response for the input signal with OFF pulse width less than PWIN(off). Please refer to Fig.7.

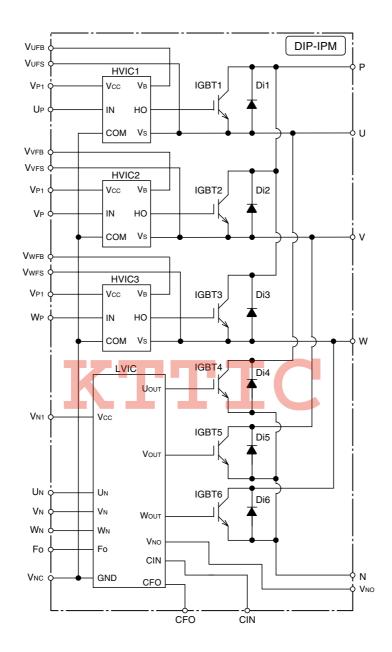

Fig. 4 THE DIP-IPM INTERNAL CIRCUIT

TRANSFER-MOLD TYPE **INSULATED TYPE**

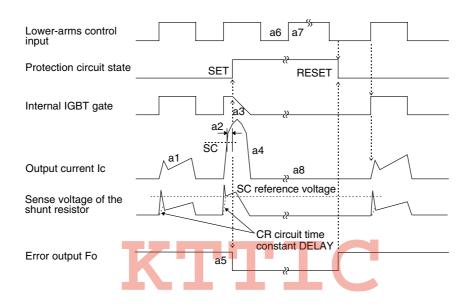

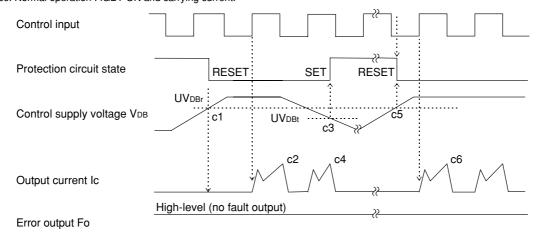

#### Fig. 5 TIMING CHART OF THE DIP-IPM PROTECTIVE FUNCTIONS

#### [A] Short-Circuit Protection (Lower-arms only with the external shunt resistor and CR filter)

- a1. Normal operation: IGBT ON and carrying current.

- a2. Short circuit current detection (SC trigger).

- a3. IGBT gate hard interruption.

- a4. IGBT turns OFF.

- a5. Fo timer operation starts: The pulse width of the Fo signal is set by the external capacitor CFo.

- a6. Input "L" : IGBT OFF.

- a7. Input "H" : IGBT ON.

- a8. IGBT OFF in spite of input "H".

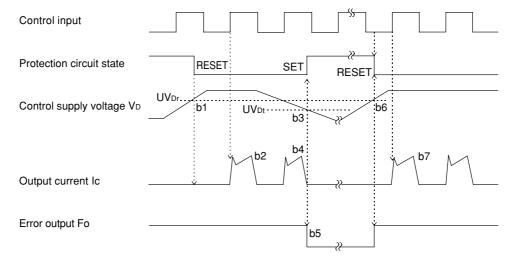

#### [B] Under-Voltage Protection (Lower-arm, UVD)

- b1. Control supply voltage rises: After the voltage level reaches UVDr, the circuits start to operate when next input is applied.

- b2. Normal operation: IGBT ON and carrying current.

- b3. Under voltage trip (UVDt).

- b4. IGBT OFF in spite of control input condition.

- b5. Fo operation starts.

- b6. Under voltage reset (UVDr).

- b7. Normal operation: IGBT ON and carrying current.

TRANSFER-MOLD TYPE **INSULATED TYPE**

#### [C] Under-Voltage Protection (Upper-arm, UVDB)

- c1. Control supply voltage rises: After the voltage reaches UVDBr, the circuits start to operate when next input is applied. c2. Normal operation: IGBT ON and carrying current.

- c3. Under voltage trip (UVDBt).

- c4. IGBT OFF in spite of control input condition, but there is no Fo signal output.

- c5. Under voltage reset (UVDBr)

- c6. Normal operation: IGBT ON and carrying current.

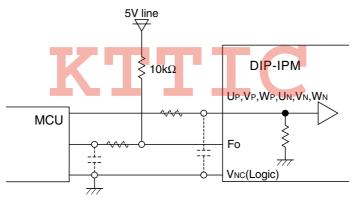

Fig. 6 RECOMMENDED CPU I/O INTERFACE CIRCUIT

Note: The setting of RC coupling at each input (parts shown dotted) depends on the PWM control scheme and the wiring impedance of the printed circuit board.

The DIP-IPM input section integrates a 2.5k $\Omega$  (min) pull-down resistor. Therefore, when using an external filtering resistor, pay attention to the turn-on threshold voltage.

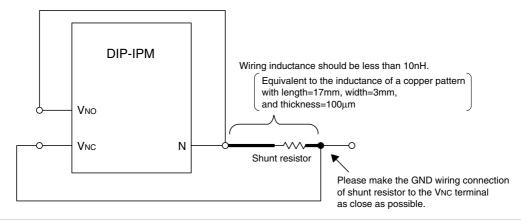

#### Fig. 7 WIRING CONNECTION OF SHUNT RESISTOR

TRANSFER-MOLD TYPE **INSULATED TYPE**

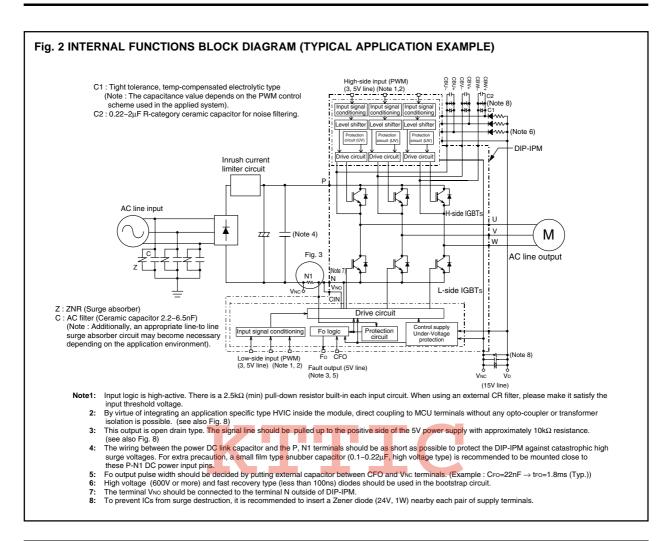

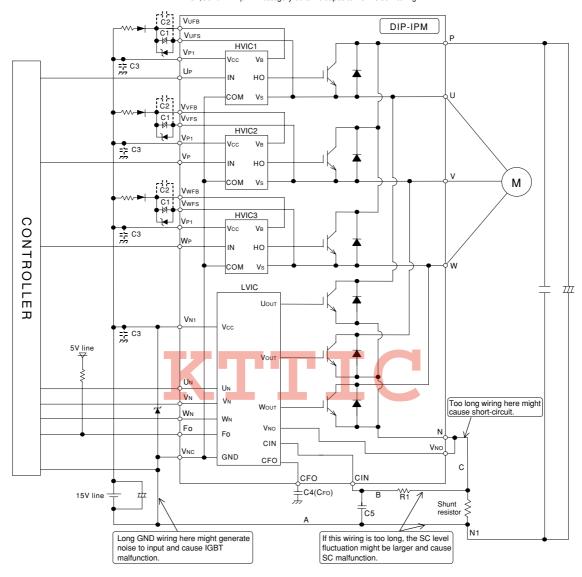

Fig. 8 TYPICAL DIP-IPM APPLICATION CIRCUIT EXAMPLE

C1:Tight tolerance temp-compensated electrolytic type C2,C3: 0.22~2µF R-category ceramic capacitor for noise filtering.

- Note 1: To prevent the input signals oscillation, the wiring of each input should be as short as possible. (Less than 2cm)

- 2: By virtue of integrating an application specific type HVIC inside the module, direct coupling to MCU terminals without any opto-coupler or transformer isolation is possible.

- 3: Fo output is open drain type. This signal line should be pulled up to the positive side of the 5V power supply with approximately 10kΩ resistor.

- **4:** Fo output pulse width is determined by the external capacitor between CFO and VNc terminals (CFo). (Example: CFo = 22 nF  $\rightarrow$  tFO = 1.8 ms (typ.))

- 5: The logic of input signal is high-active. The DIP-IPM input signal section integrates a  $2.5k\Omega$  (min) pull-down resistor. Therefore, when using external filtering resistor, care must be taken to satisfy the turn-on threshold voltage requirement.

- **6**: To prevent malfunction of protection, the wiring of A, B, C should be as short as possible.

- 7: Please set the C5R1 time constant in the range  $1.5\sim2\mu s$ .

- 8: Each capacitor should be located as nearby the pins of the DIP-IPM as possible.

- 9: To prevent surge destruction, the wiring between the smoothing capacitor and the P, N1 pins should be as short as possible. Approximately a 0.1~0.22μF snubber capacitor between the P-N1 pins is recommended.

- 10: The terminal VNO should be connected with the terminal N outside.

- 11: To prevent ICs from surge destruction, it is recommended to insert a Zener diode (24V, 1W) nearby each pair of supply terminals.