Low Noise, 300mA and 500mA CMOS LDO Regulators

#### **FEATURES**

- Very Low Dropout Voltage: 0.6Ω PMOS Pass Device

- Accurate Output Voltage: 2% over Temperature

- Guaranteed 500mA Output Current: SP6205

- Ultra Low Noise Output: 12µV<sub>RMS</sub> with 10nF Bypass

- Unconditionally Stable with 2.2µF Ceramic

- Low Quiescent Current: 45µA

- Very Low Ground Current: 350µA at 500 mA

- Power-Saving Shutdown Mode: < 1µA

- Fast Turn-On and Turn-Off: 60µS

- Fast Transient Response

- Current Limit and Thermal Shutdown Protection

- Very Good Load/Line Regulation: 0.07/0.04%

- Excellent PSRR: 67dB < 1kHz

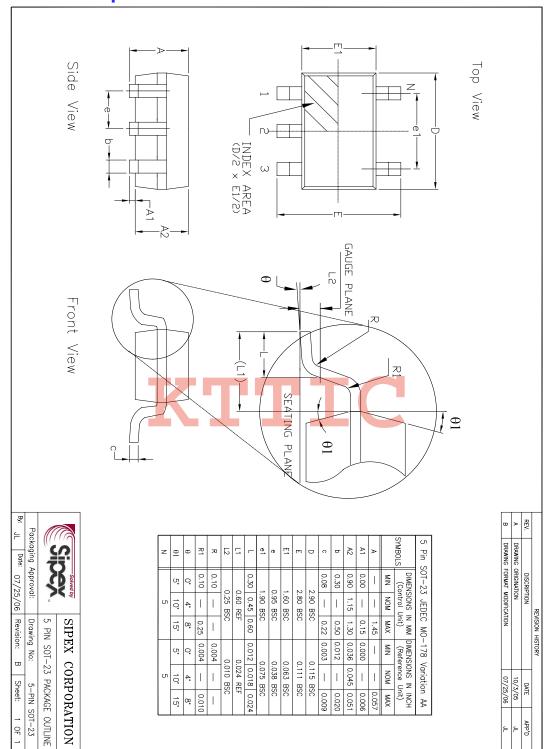

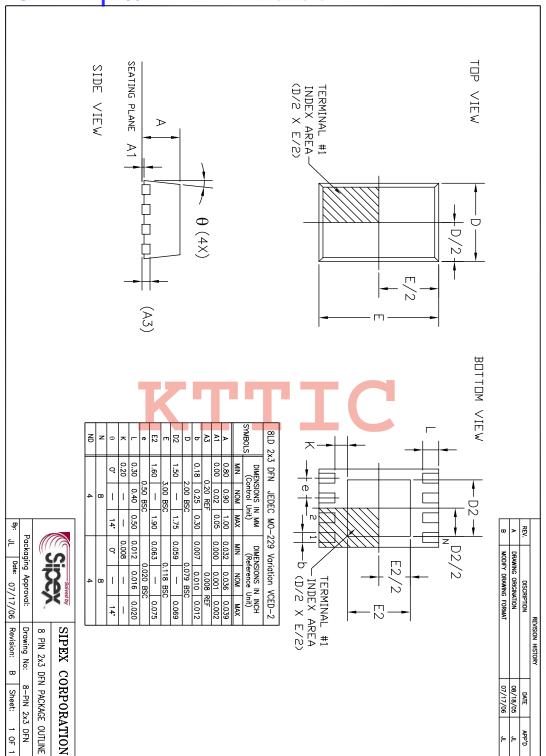

- Industry Standard SOT-23-5 and Small 8 pin 2X3 DFN Package

- Fixed Output Voltages: 2.5V, 2.7V, 2.8V, 2.85V, 3.0V and 3.3V

- Adjustable Output Available

Now Available in Lead Free Packaging

# **APPLICATIONS**

- Cellular / GSM Phones

- Laptop / Palmtop Computers

- Battery-Powered Systems

- Pagers

- Medical Devices

- MP3/CD Players

- Digital Still Cameras

DESCRIPTION

The SP6203/6205 are ultra low noise CMOS LDOs with very low dropout and ground current. The noise performance is achieved by means of an external bypass capacitor without sacrificing turn-on and turn-off speed critical to portable applications. Extremely stable and easy to use, these devices offer excellent PSRR and Line/Load regulation. Target applications include battery-powered equipment such as portable and wireless products. Regulators' ground current increases only slightly in dropout. Fast turn-on/turn-off enable control and an internal  $30\Omega$  pull down on output allows quick discharge of output even under no load conditions. Both LDOs are protected with current limit and thermal shutdown.

Both LDOs are available in fixed & adjustable output voltage versions and come in an industry standard SOT-23 5-pin and small 2X3 8pin DFN packages. For SC-70 100mA CMOS LDO, SP6213 is available.

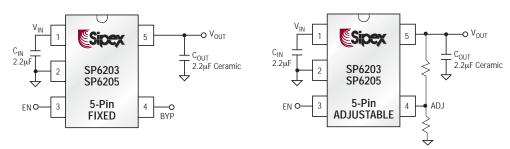

#### TYPICAL APPLICATION CIRCUIT

# KTTIC ABSOLUTE IN AND MANY IN LEST LIC. COM

### **OPERATING RATINGS**

| nput Voltage (V <sub>IN</sub> )2V to 6V               | Supply Input Voltage |

|-------------------------------------------------------|----------------------|

| oltage (V <sub>OUT</sub> )0.6V to V <sub>IN</sub> +1V | Output Voltage (Vo   |

| nput Voltage (V <sub>EN</sub> )2V to 6V               | Enable Input Volta   |

| issipation (PD)Internally Limited, Note 1             | Power Dissipation    |

| emperature (soldering 5s)+260°C                       | Lead Temperature     |

| Temperature65°C to +150°C                             | Storage Temperati    |

| Temperature +150°C                                    | Junction Tempera     |

| Input Voltage (V <sub>m</sub> ) | +2.7V to +5.5V |

|---------------------------------|----------------|

|                                 | 0 to 5.5V      |

|                                 | 40°C to +125°C |

|                                 | ,,)Note 1      |

| Thermal Resistance, SOT-23-6 (0 | Note 1         |

Remark: The device is not guaranteed to function outside its operating rating.

These are stress ratings only and functional operation of the device at these ratings or any other above those indicated in the operation sections of the specifications below is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

#### ELECTRICAL SPECIFICATIONS

Unless otherwise specified:  $V_{IN}=V_{OUT}+0.5V$  to 6V,  $C_{OUT}=2.2\mu F$  ceramic,  $C_{IN}=2.2\mu F$ ,  $I_{OUT}=100\mu A$ ,  $-40^{\circ}C < T < 125^{\circ}C$ . The  $\blacklozenge$  denotes the specifications which apply over full operating temperature range -40°C to +125°C, unless otherwise specified.

| PARAMETER                                                    | MIN          | TYP                             | MAX        | UNITS             | <b>*</b> | CONDITIONS                                                                                                                                                                            |

|--------------------------------------------------------------|--------------|---------------------------------|------------|-------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input Voltage                                                |              |                                 | 6          | V                 | <b>*</b> |                                                                                                                                                                                       |

| Output Voltage Accuracy                                      | -2           |                                 | +2         | %                 | <b>*</b> | Variation from specified V <sub>OUT</sub>                                                                                                                                             |

| Output Voltage<br>Temperature Coefficient, Note2             |              | 50                              |            | ppm/°C            |          | $\Delta V_{OUT}/\Delta T$                                                                                                                                                             |

| Reference Voltage                                            | 1.225        | 1.25                            | 1.275      | V                 | <b>*</b> | Adjustable version only                                                                                                                                                               |

| Line Regulation                                              |              | 0.04                            | 0.3        | %/V               |          | ΔV <sub>OUT</sub> (V <sub>IN</sub> below 6V)                                                                                                                                          |

| Load Regulation, Note 3                                      |              | 0.07<br>0.13                    | 0.3<br>0.5 | %                 |          | I <sub>OUT</sub> = 0.1mA to 300mA (SP6203)<br>I <sub>OUT</sub> = 0.1mA to 500mA (SP6205)                                                                                              |

| Dropout Voltage for $V_{OUT} \ge 3.0V$ , Note 4              |              | 0.06<br>60<br>120<br>180<br>300 | 300<br>500 | mV                | •        | I <sub>OUT</sub> = 0.1mA<br>I <sub>OUT</sub> = 100mA<br>I <sub>OUT</sub> = 200mA<br>I <sub>OUT</sub> = 300mA (SP6203)<br>I <sub>OUT</sub> = 500mA (SP6205)                            |

| Ground Pin Current, Note 5                                   |              | 45<br>110<br>175<br>235<br>350  | 330<br>490 | μА                |          | I <sub>OUT</sub> = 0.1mA (I <sub>QUIESCENT</sub> )<br>I <sub>OUT</sub> = 100mA<br>I <sub>OUT</sub> = 200mA<br>I <sub>OUT</sub> = 300mA (SP6203)<br>I <sub>OUT</sub> = 500mA (SP6205)  |

| Shutdown Supply Current                                      |              | 0.01                            | 1          | μΑ                | <b>*</b> | V <sub>EN</sub> < 0.4V (shutdown)                                                                                                                                                     |

| Current Limit                                                | 0.33<br>0.55 | 0.50<br>0.85                    | 0.8<br>1.4 | Α                 |          | V <sub>OUT</sub> = ZeroV (SP6203)<br>V <sub>OUT</sub> = ZeroV (SP6205)                                                                                                                |

| Thermal Shutdown Junction<br>Temperature                     |              | 170                             |            | °C                |          | Regulator Turns off                                                                                                                                                                   |

| Thermal Shutdown Hysteresis                                  |              | 12                              |            | °C                |          | Regulator turns on again at 158°C                                                                                                                                                     |

| Power Supply Rejection Ratio                                 |              | 67                              |            | dB                |          | f ≤ 1kHz                                                                                                                                                                              |

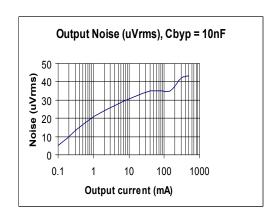

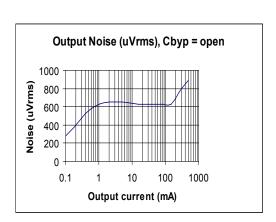

| Output Noise Voltage, Note 6                                 |              | 150<br>630<br>12<br>50          | 75         | μV <sub>RMS</sub> |          | $\begin{array}{c} C_{BYP} = 0 nF, \ I_{OUT} = 0.1 mA \\ C_{BYP} = 0 nF, \ I_{OUT} = 300 mA \\ C_{BYP} = 10 nF, \ I_{OUT} = 0.1 mA \\ C_{BYP} = 10 nF, \ I_{OUT} = 300 mA \end{array}$ |

| Thermal Regulation, Note 7                                   |              | 0.05                            |            | %/W               |          | $\Delta V_{OUT}/\Delta P_{D}$                                                                                                                                                         |

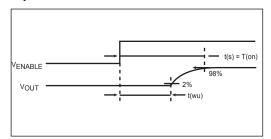

| Wake-Up Time (T <sub>WU</sub> ), Note 8 (from shutdown mode) |              | 25                              | 50         | μS                |          | $V_{IN} \ge 4V$ , Note 10<br>$I_{OUT} = 30$ mA                                                                                                                                        |

| Turn-On Time (T <sub>ON</sub> ), Note 9 (from shutdown mode) |              | 60                              | 120        | μS                |          | $V_{IN} \ge 4V$ , Note 10<br>$I_{OUT} = 30$ mA                                                                                                                                        |

| Turn-Off Time (T <sub>OFF</sub> ),                           |              | 100<br>15                       | 250<br>25  | μS                |          | $I_{OUT} = 0.1 \text{mA}, V_{IN} \ge 4 \text{V}, \text{ Note } 10$<br>$I_{OUT} = 300 \text{mA}, V_{IN} \ge 4 \text{V}, \text{ Note } 10$                                              |

| Output Discharge Resistance                                  |              | 30                              |            | Ω                 |          | No Load                                                                                                                                                                               |

| Enable Input Logic Low Voltage                               |              |                                 | 0.4        | V                 | <b>*</b> | Regulator Shutdown                                                                                                                                                                    |

| Enable Input Logic High Voltage                              | 1.6          |                                 |            | V                 | <b>*</b> | Regulator Enabled                                                                                                                                                                     |

# KTTIC http://www.ktticecomcal specifications notes

Note 1: Maximum power dissipation can be calculated using the formula:  $P_D = (T_{J(max)} - T_A) / \theta_{JA}$ , where  $T_{J(max)}$  is the junction temperature,  $T_A$  is the ambient temperature and  $\theta_{JA}$  is the junction-to-ambient thermal resistance.  $\theta_{JC}$  is 6°C/W for this package. Exceeding the maximum allowable power dissipation will result in excessive die temperature and the regulator will go into thermal shutdown mode.  $\theta_{JA}$  is 191°C/W for SOT-23-5, and is 59°C/W for the 8-pin DFN. A part mounted on a PC board will deliver improved thermal performance based upon copper surface area.

**Note 2:** Output voltage temperature coefficient is defined as the worst case voltage change divided by the total temperature range.

**Note 3:** Regulation is measured at constant junction temperature using low duty cycle pulse testing. Changes in output voltage due to heating effects are covered by the thermal regulation specification.

**Note 4:** Dropout-voltage is defined as the input to output differential at which the output voltage drops 2% below its nominal value measured at 1V differential.

**Note 5:** Ground pin current is the regulator quiescent current. The total current drawn from the supply is the sum of the load current plus the ground pin current.

**Note 6:** Output noise voltage is defined within a certain bandwidth, namely 10Hz < BW < 100kHz. An external bypass cap (10nF) from reference output (BYP pin) to ground significantly reduces noise at output.

**Note 7:** Thermal regulation is defined as the change in output voltage at a time "t" after a change in power dissipation is applied, excluding load and line regulation effects. Specifications are for a 300mA load pulse at  $V_{IN}$  = 6V for t = 1ms.

**Note 8:** The wake-up time  $(T_{WU})$  is defined as the time it takes for the output to start rising after enable is brought high.

**Note 9:** The total turn-on time is called the settling time  $(T_S)$ , which is defined as the condition when both the output and the bypass node are within 2% of their fully enabled values when released from shutdown.

Note 10: For output voltage versions requiring VIN to be lower than 4V, timing (ToN & ToFF) increases slightly.

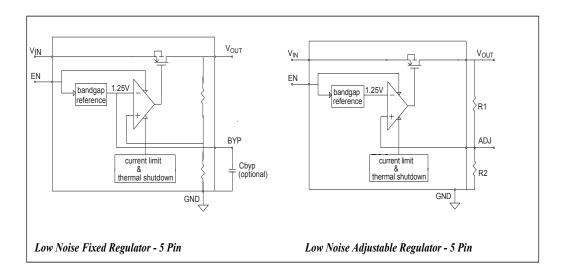

### **FUNCTIONAL DIAGRAM**

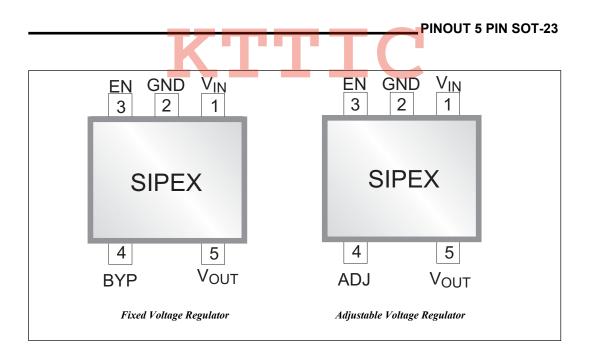

### **5 PIN OPTION**

| PIN NUMBER | NAME             | FUNCTION                                                                                                  |  |  |

|------------|------------------|-----------------------------------------------------------------------------------------------------------|--|--|

| 1          | V <sub>IN</sub>  | Power Supply Input                                                                                        |  |  |

| 2          | GND              | Ground Terminal                                                                                           |  |  |

| 3          | EN               | Enable/Shutdown (Logic high = enable, logic low = shutdown)                                               |  |  |

| 4 (Fixed)  | ВҮР              | Reference bypass input for ultra-quiet operat Connecting a 10nF cap on this pin reduces output noise.     |  |  |

| 4 (adj.)   | ADJ              | Adjustable (Input): Adjustable regulator feed-back input. Connect to a resistive voltage-divider network. |  |  |

| 5          | V <sub>OUT</sub> | Regulator Output Voltage                                                                                  |  |  |

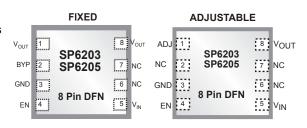

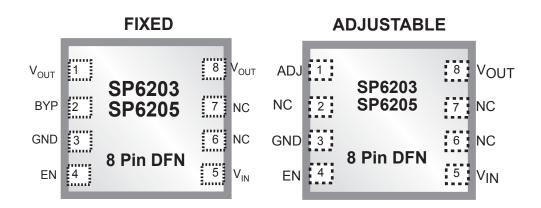

#### **8 PIN OPTION**

| 8 PIN DFN PIN CONFIGURATION |                  |                                                                                                                   |  |

|-----------------------------|------------------|-------------------------------------------------------------------------------------------------------------------|--|

| PIN NUMBER                  | NAME             | FUNCTION                                                                                                          |  |

| 1(fixed)                    | V <sub>OUT</sub> | Regulator Output Voltage. Connect to Pin 8 Vout.                                                                  |  |

| 1(Adj)                      | ADJ              | Adjustable (Input): Adjustable regulator feed-<br>back input. Connect to a resistive voltage-<br>divider network. |  |

| 2(fixed)                    | ВҮР              | Reference bypass input for ultra-quiet operation. Connecting a 10nF cap on this pin reduces output noise.         |  |

| 2(Adj)                      | NC               | No Connect                                                                                                        |  |

| 3                           | GND              | Ground                                                                                                            |  |

| 4                           | EN               | Enable/Shutdown (Logic high = enable, logic low = shutdown)                                                       |  |

| 5                           | V <sub>IN</sub>  | Power Supply Input                                                                                                |  |

| 6                           | NC               | No Connect                                                                                                        |  |

| 7                           | NC               | No Connect                                                                                                        |  |

| 8                           | V <sub>OUT</sub> | Regulator Output VoltageA                                                                                         |  |

### **PINOUT 8 PIN DFN**

# KTT-IC http://www.kttipal.eerpreance characteristics

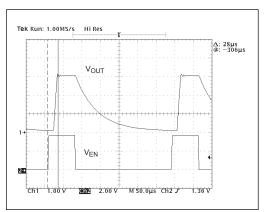

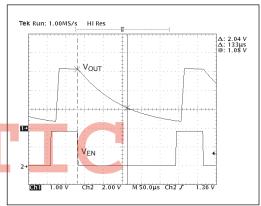

Turn on Time,  $R_{LOAD} = 50\Omega$  (60mA)

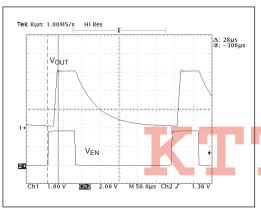

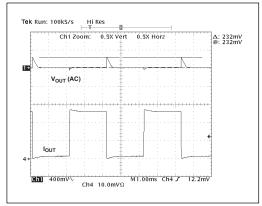

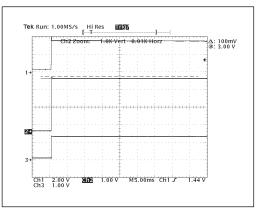

Turn off Time,  $R_{LOAD} = 6\Omega$  (500mA)

Turn off Time,  $R_{LOAD} = 30K (0.1mA)$

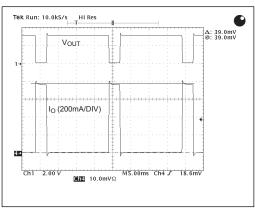

Load Regulation,  $I_o = 100 \mu A \sim 500 mA$

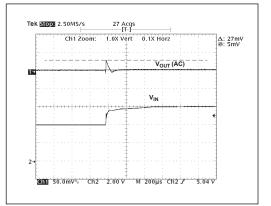

Line Regulation, Line Step from 4V to 6V,  $I_o = 1$ mA

# KTTIC http://www.priggl.pertpringercharacteristics: Continued

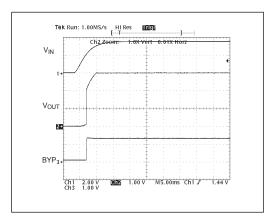

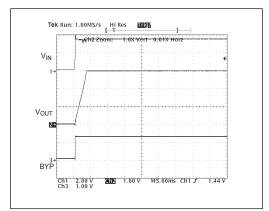

Start Up Waveform,  $V_{IN} = 3.5V$ ,  $I_o = 500 \text{mA}$

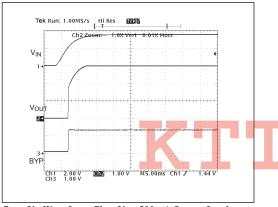

Start Up Waveform, Slow  $V_{{\mbox{\scriptsize IN}}}$ , No Load

Start Up Waveform, Slow  $V_{IN}$ , 500mA Output Load

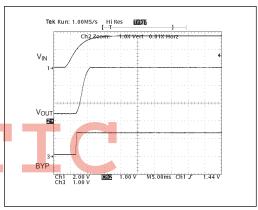

Start Up Waveform, Slow V<sub>IN</sub>, C<sub>OUT</sub>=1000µF, I<sub>O</sub>=0mA

Start Up Waveform, Slow  $V_{\rm IN}$ ,  $C_{\rm OUT}$ =1000 $\mu$ F,  $I_{\rm o}$ =500mA

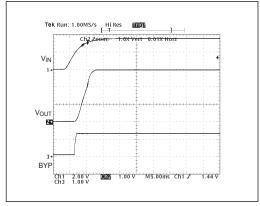

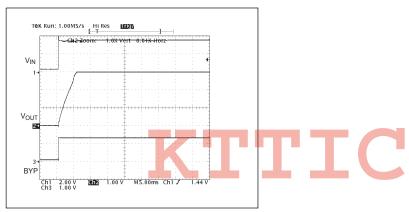

Fast V<sub>IN</sub>, No Load

# TT-C http://wyrigak.performance.characteristics: Continued

Fast V<sub>IN</sub>, 500mA Output Load

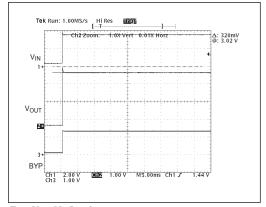

Fast  $V_{IN} = 1000 \mu F$  Output Load

Fast  $V_{IN}$ ,  $C_{OUT}$ =1000 $\mu$ F,  $I_{o}$ =500mA

# KTTIC http://www.kttic.com theory of operation

#### **General Overview**

The SP6203/6205 is intended for applications where very low dropout voltage, low supply current and low output noise are critical, even with high load conditions (500mA maximum).

Unlike bipolar regulators, the SP6203/6205 (CMOS LDO) supply current increases only slightly with load current.

The SP6203/6205 contains an internal bandgap reference which is fed into the inverting input of the LDO-amplifier. The output voltage is then set by means of a resistor divider and compared to the bandgap reference voltage. The error LDO-amplifier drives the gate of a P-channel MOSFET pass device that has a  $R_{\rm DS(ON)}$  of  $0.6\Omega$  at 500 mA producing a 300 mV drop at the output.

Furthermore, the SP6203/6205 has its own current limit circuitry (500mA/850mA) to ensure that the output current will not damage the device during output short, overload or start-up.

Also, the SP6203/6205 includes thermal shutdown circuitry to turn off the device when the junction temperature exceeds 170°C and it remains off until the temperature drops by 12°C.

### **Enable/Shutdown Operation**

The SP6203/6205 is turned off by pulling the  $V_{\rm EN}$  pin below 0.4V and turned on by pulling it above 1.6V.

If this enable/shutdown feature is not required, it should be tied directly to the input supply voltage to keep the regulator output on at all time.

While in shutdown,  $V_{OUT}$  quickly falls to zero (turn-off time is dependent on load conditions and output capacitance on  $V_{OUT}$ ) and power consumption drops nearly to zero.

### **Input Capacitor**

A small capacitor of  $2.2\mu F$  is required from  $V_{\rm IN}$  to GND if a battery is used as the power source. Any good quality electrolytic, ceramic or tantalum capacitor may be used at the input.

#### **Output Capacitor**

An output capacitor is required between  $V_{OUT}$  and GND to prevent oscillation. A 2.2 $\mu$ F output capacitor is recommended.

Larger values make the chip more stable which means an improvement of the regulator's transient response. Also, when operating from other sources than batteries, supply-noise rejection can be improved by increasing the value of the input and output capacitors and using passive filtering techniques.

For a lower output current, a smaller output capacitance can be chosen.

Finally, the output capacitor should have an effective series resistance (ESR) of  $0.5\Omega$  or less.

Therefore, the use of good quality ceramic or tantalum capacitors is advised.

## **Bypass Capacitor**

A bypass pin (BYP) is provided to decouple the bandgap reference. A 10nF external capacitor connected from BYP to GND reduces noise present on the internal reference, which in turn significantly reduces output noise and also improves power supply rejection. Note that the minimum value of C<sub>OUT</sub> must be increased to maintain stability when the bypass capacitor is used because C<sub>BYP</sub> reduces the regulator phase margin. If output noise is not a concern, this input may be left unconnected. Larger capacitor values may be used to further improve power supply rejection, but result in a longer time period (slower turn on) to settle output voltage when power is initially applied.

### No Load Stability

The SP6203/6205 will remain stable and in regulation with no external load (other than the internal voltage driver) unlike many other voltage regulators. This is especially important in CMOS RAM battery back-up applications.

# KTTIC http://www.kttic.@@RMOF OPERATION: Continued

#### **Turn On Time**

The turn on response is split up in two separate response categories: the wake up time  $(T_{WU})$  and the settlling time  $(T_S)$ . The wake up time is defined as the time it takes for the output to rise to 2% of its total value after being released from shutdown  $(E_N > 0.4V)$ . The settling time is defined as the condition where the output reaches 98% of its total value after being released from shutdown. The latter is also called the turn on time and is dependent on the output capacitor, a little bit on load and, if present, on a bypass capacitor.

#### **Turn Off Time**

The turn off time is defined as the condition where the output voltage drops about 66% ( $\theta$ ) of its total value. 50 to 70 is the constant where the output voltage drops nearly to zero. There will always be a small voltage drop in shutdown because of the switch unless we short-circuit it. The turn off time of the output voltage is dependent on load conditions, output capacitance on  $V_{OUT}$  (time constant  $\tau = R_L C_L$ ) and also on the difference in voltage between input and output.

#### **Thermal Considerations**

The SP6203/6205 is designed to provide 300/500 mA of continuous current in a tiny package. Maximum power dissipation can be calculated based on the output current and the voltage drop across the part. To determine the maximum power dissipation of the package, use the junction-to-ambient thermal resistance of the device and the following basic equation:

$$P_D = (T_{I(max)} - T_A) / \theta J_A$$

$T_{J(max)}$  is the maximum junction temperature of the die and is 125°C.  $T_A$  is the ambient temperature.  $\theta_{JA}$  is the junction-to-ambient thermal resistance for the regulator and is layout dependent. The SOT-23-5 package has a  $\theta_{JA}$  of approximately 256°C/W for minimum PCB copper footprint area.

This results in a maximum power dissipation of:  $P_{D(max)} = [(125^{\circ}C - 25^{\circ}C)/(191^{\circ}C/W)] = 523mW$

The actual power dissipation of the regulator circuit can be determined using one simple equation:

$$P_D = (V_{IN} - V_{OUT}) * I_{OUT} + V_{IN} * I_{GND}$$

To prevent the device from entering thermal shutdown maximum power dissipation can not be exceeded.

Substituting  $P_{D(max)}$  for  $P_D$  and solving for the operating conditions that are critical to the application will give the maximum operating conditions for the regulator circuit. For example, if we are operating the SP6203 3.0V at room temperature, with a minimum footprint layout and and output current of 300mA, the maximum input voltage can be determined, based on the equation below. Ground pin current can be taken from the electrical specifications table (0.23mA at 300mA).

$390 \text{mW} = (V_{\text{IN}} - 3.0 \text{V}) * 300 \text{mA} + V_{\text{IN}} * 0.23 \text{mA}$

After calculations, we find that the maximum input voltage of a 3.0V application at 300mA of output current in a SOT-23-5 package is 4.7V.

So if the intend is to operate a 5V output version from a 6V supply at 300mA load and at a 25°C ambient temperature, then the actual total power dissipation will be:

$P_D = ([6V-5V]*[300mA])+(6V*0.23mA)=301.4mW$

This is well below the 523mW package maximum. Therefore, the regulator can be used.

# KTTIC http://www.kttic.chefm of Operation: Continued

Note that the regulator cannot always be used at its maximum current rating. For example, in a 5V input to 3.0V output application at an ambient temperature of 25°C and operating at the full 500mA (I<sub>GND</sub> = 0.355mA) load, the regulator is limited to a much lower load current, determined by the following equation:

$$523\text{mW} = ([5\text{V}-3\text{V}]*[I_{load(max)}])+(5\text{V}*0.350\text{mA})$$

After calculation, we find that in such an application (SP6205) the regulator is limited to 260.6mA. Doing the same calculations for the 300mA LDO (SP6203) will limit the regulator's output current to 260.9mA.

Also, taking advantage of the very low dropout voltage characteristics of the SP6203/6205, power dissipation can be reduced by using the lowest possible input voltage to minimize the input-to-output drop.

### **Adjustable Regulator Applications**

The SP6203/6205 can be adjusted to a specific output voltage by using two external resistors (see functional diagram). The resistors set the output voltage based on the following equation:

$$V_{OUT} = V_{REF} * (R1/R2 + 1)$$

Resistor values are not critical because ADJ (adjust) has a high input impedance, but for best performance use resistors of  $470 \text{K}\Omega$  or less. A bypass capacitor from ADJ to  $V_{OUT}$  provides improved noise performance.

### **Dual-Supply Operation**

When used in dual supply systems where the regulator load is returned to a negative supply, the output voltage must be diode clamped to ground.

#### **Layout Considerations**

The primary path of heat conduction out of the package is via the package leads. Therefore, careful considerations have to be taken into account:

- 1) Attaching the part to a larger copper footprint will enable better heat transfer from the device, especially on PCB's where there are internal ground and power planes.

- 2) Place the input, output and bypass capacitors close to the device for optimal transient response and device behavior.

- 3) Connect all ground connections directly to the ground plane. In case there's no ground plane, connect to a common local ground point before connecting to board ground.

Such layouts will provide a much better thermal conductivity (lower  $\theta_{JA}$ ) for, a higher maximum allowable power dissipation limit.

# KTTIC http://www.kttic.compackage: 5Pin SOT-23

KTTIC http://www.kttic.com Package: 8Pin DFN

KTTIC http://www.kttic.coprpering information

| Part Number       | Top<br>Marking           | Temperature<br>Range | Voltage<br>Option | Package<br>Type |

|-------------------|--------------------------|----------------------|-------------------|-----------------|

| SP6203EM5-1-8     | N2WW                     | -40°C to +125°C      | 1.8V              | 5 Pin SOT-23    |

| SP6203EM5-1-8/TR  | N2WW                     | -40°C to +125°C      | 1.8V              | 5 Pin SOT-23    |

| SP6203EM5-2-5     | L2WW                     | -40°C to +125°C      | 2.5V              | 5 Pin SOT-23    |

| SP6203EM5-2-5/TR  | L2WW                     | -40°C to +125°C      | 2.5V              | 5 Pin SOT-23    |

| SP6203EM5-2-7     | G2WW                     | -40°C to +125°C      | 2.7V              | 5 Pin SOT-23    |

| SP6203EM5-2-7/TR  | G2WW                     | -40°C to +125°C      | 2.7V              | 5 Pin SOT-23    |

| SP6203EM5-2-8     | Q3WW                     | -40°C to +125°C      | 2.8V              | 5 Pin SOT-23    |

| SP6203EM5-2-8/TR  | Q3WW                     | -40°C to +125°C      | 2.8V              | 5 Pin SOT-23    |

| SP6203EM5-2-85    | H2WW                     | -40°C to +125°C      | 2.85V             | 5 Pin SOT-23    |

| SP6203EM5-2-85/TR | H2WW                     | -40°C to +125°C      | 2.85V             | 5 Pin SOT-23    |

| SP6203EM5-3-0     | M2WW                     | -40°C to +125°C      | 3.0V              | 5 Pin SOT-23    |

| SP6203EM5-3-0/TR  | M2WW                     | -40°C to +125°C      | 3.0V              | 5 Pin SOT-23    |

| SP6203EM5-3-3     | J2WW                     | -40°C to +125°C      | 3.3V              | 5 Pin SOT-23    |

| SP6203EM5-3-3/TR  | J2WW                     | -40°C to +125°C      | 3.3V              | 5 Pin SOT-23    |

| SP6203EM5         | Q2WW                     | -40°C to +125°C      | ADJ               | 5 Pin SOT-23    |

| SP6203EM5/TR      | Q2WW                     | -40°C to +125°C      | ADJ               | 5 Pin SOT-23    |

| SP6203ER-1-8      | 620 <mark>318YW</mark> W | -40°C to +125°C      | 1.8V              | 8 Pin DFN       |

| SP6203ER-1-8/TR   | 620318YWW                | -40°C to +125°C      | 1.8V              | 8 Pin DFN       |

| SP6203ER-2-5      | 620325YWW                | -40°C to +125°C      | 2.5V              | 8 Pin DFN       |

| SP6203ER-2-5/TR   | 620325YWW                | -40°C to +125°C      | 2.5V              | 8 Pin DFN       |

| SP6203ER-2-7      | 620327YWW                | -40°C to +125°C      | 2.7V              | 8 Pin DFN       |

| SP6203ER-2-7/TR   | 620327YWW                | -40°C to +125°C      | 2.7V              | 8 Pin DFN       |

| SP6203ER-2-8      | 620328YWW                | -40°C to +125°C      | 2.8V              | 8 Pin DFN       |

| SP6203ER-2-8/TR   | 620328YWW                | -40°C to +125°C      | 2.8V              | 8 Pin DFN       |

| SP6203ER-2-85     | 620385YWW                | -40°C to +125°C      | 2.85V             | 8 Pin DFN       |

| SP6203ER-2-85/TR  | 620385YWW                | -40°C to +125°C      | 2.85V             | 8 Pin DFN       |

| SP6203ER-3-0      | 620330YWW                | -40°C to +125°C      | 3.0V              | 8 Pin DFN       |

| SP6203ER-3-0/TR   | 620330YWW                | -40°C to +125°C      | 3.0V              | 8 Pin DFN       |

| SP6203ER-3-3      | 620333YWW                | -40°C to +125°C      | 3.3V              | 8 Pin DFN       |

| SP6203ER-3-3/TR   | 620333YWW                | -40°C to +125°C      | 3.3V              | 8 Pin DFN       |

| SP6203ER          | 6203ERYWW                | -40°C to +125°C      | ADJ               | 8 Pin DFN       |

| SP6203ER/TR       | 6203ERYWW                | -40°C to +125°C      | ADJ               | 8 Pin DFN       |

# KTTIC http://www.kttic.copprdering information

| Part Number       | Top<br>Marking | Temperature<br>Range | Voltage<br>Option | Package<br>Type |  |  |  |

|-------------------|----------------|----------------------|-------------------|-----------------|--|--|--|

| SP6205EM5-1-8     | X2WW           | -40°C to +125°C      | 1.8V              | 5 Pin SOT-23    |  |  |  |

| SP6205EM5-1-8/TR  | X2WW           | -40°C to +125°C      | 1.8V              | 5 Pin SOT-23    |  |  |  |

| SP6205EM5-2-5     | V2WW           | -40°C to +125°C      | 2.5V              | 5 Pin SOT-23    |  |  |  |

| SP6205EM5-2-5/TR  | V2WW           | -40°C to +125°C      | 2.5V              | 5 Pin SOT-23    |  |  |  |

| SP6205EM5-2-7     | R2WW           | -40°C to +125°C      | 2.7V              | 5 Pin SOT-23    |  |  |  |

| SP6205EM5-2-7/TR  | R2WW           | -40°C to +125°C      | 2.7V              | 5 Pin SOT-23    |  |  |  |

| SP6205EM5-2-8     | E3WW           | -40°C to +125°C      | 2.8V              | 5 Pin SOT-23    |  |  |  |

| SP6205EM5-2-8/TR  | E3WW           | -40°C to +125°C      | 2.8V              | 5 Pin SOT-23    |  |  |  |

| SP6205EM5-2-85    | S2WW           | -40°C to +125°C      | 2.85V             | 5 Pin SOT-23    |  |  |  |

| SP6205EM5-2-85/TR | S2WW           | -40°C to +125°C      | 2.85V             | 5 Pin SOT-23    |  |  |  |

| SP6205EM5-3-0     | W2WW           | -40°C to +125°C      | 3.0V              | 5 Pin SOT-23    |  |  |  |

| SP6205EM5-3-0/TR  | W2WW           | -40°C to +125°C      | 3.0V              | 5 Pin SOT-23    |  |  |  |

| SP6205EM5-3-3     | T2WW           | -40°C to +125°C      | 3.3V              | 5 Pin SOT-23    |  |  |  |

| SP6205EM5-3-3/TR  | T2WW           | -40°C to +125°C      | 3.3V              | 5 Pin SOT-23    |  |  |  |

| SP6205EM5         | A3WW           | -40°C to +125°C      | ADJ               | 5 Pin SOT-23    |  |  |  |

| SP6205EM5 /TR     | A3WW           | -40°C to +125°C      | ADJ               | 5 Pin SOT-23    |  |  |  |

|                   |                |                      |                   |                 |  |  |  |

| SP6205ER-1-8      | 620518YWW      | -40°C to +125°C      | 1.8V              | 8 Pin DFN       |  |  |  |

| SP6205ER-1-8/TR   | 620518YWW      | -40°C to +125°C      | 1.8V              | 8 Pin DFN       |  |  |  |

| SP6205ER-2-5      | 620525YWW      | -40°C to +125°C      | 2.5V              | 8 Pin DFN       |  |  |  |

| SP6205FR-2-5/TR   | 620525YWW      | -40°C to +125°C      | 2.5V              | 8 Pin DFN       |  |  |  |

| SP6205ER-1-8     | 620518YWW | -40°C to +125°C | 1.8V  | 8 Pin DFN |

|------------------|-----------|-----------------|-------|-----------|

| SP6205ER-1-8/TR  | 620518YWW | -40°C to +125°C | 1.8V  | 8 Pin DFN |

| SP6205ER-2-5     | 620525YWW | -40°C to +125°C | 2.5V  | 8 Pin DFN |

| SP6205ER-2-5/TR  | 620525YWW | -40°C to +125°C | 2.5V  | 8 Pin DFN |

| SP6205ER-2-7     | 620527YWW | -40°C to +125°C | 2.7V  | 8 Pin DFN |

| SP6205ER-2-7/TR  | 620527YWW | -40°C to +125°C | 2.7V  | 8 Pin DFN |

| SP6205ER-2-8     | 620528YWW | -40°C to +125°C | 2.8V  | 8 Pin DFN |

| SP6205ER-2-8/TR  | 620528YWW | -40°C to +125°C | 2.8V  | 8 Pin DFN |

| SP6205ER-2-85    | 620585YWW | -40°C to +125°C | 2.85V | 8 Pin DFN |

| SP6205ER-2-85/TR | 620585YWW | -40°C to +125°C | 2.85V | 8 Pin DFN |

| SP6205ER-3-0     | 620530YWW | -40°C to +125°C | 3.0V  | 8 Pin DFN |

| SP6205ER-3-0/TR  | 620530YWW | -40°C to +125°C | 3.0V  | 8 Pin DFN |

| SP6205ER-3-3     | 620533YWW | -40°C to +125°C | 3.3V  | 8 Pin DFN |

| SP6205ER-3-3/TR  | 620533YWW | -40°C to +125°C | 3.3V  | 8 Pin DFN |

| SP6205ER         | 6205ERYWW | -40°C to +125°C | ADJ   | 8 Pin DFN |

| SP6205ER /TR     | 6205ERYWW | -40°C to +125°C | ADJ   | 8 Pin DFN |

# KTTIC http://www.kttic.com

# For further assistance:

Application note and calculator file for Thermal considerations with Linear Regulators:

ANP 2 <u>LDO Thermal Considerations for Linear Regulators</u> [PDF]

ANP 3 <u>LDO Linear Regulator Heat Calculator</u> [Excel]

Email: <u>Sipexsupport@sipex.com</u>

WWW Support page: <a href="http://www.sipex.com/content.aspx?p=support">http://www.sipex.com/content.aspx?p=support</a>

Sipex Application Notes: <a href="http://www.sipex.com/applicationNotes.aspx">http://www.sipex.com/content.aspx?p=support</a>

Sipex Corporation

Headquarters and Sales Office 233 South Hillview Drive Milpitas, CA 95035 TEL: (408) 934-7500 FAX: (408) 935-7600

Sipex Corporation reserves the right to make changes to any products described herein. Sipex does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others.