### Features

- High-performance, Low-power AVR<sup>®</sup> 8-bit Microcontroller

- Advanced RISC Architecture

- 130 Powerful Instructions Most Single-clock Cycle Execution

- 32 x 8 General Purpose Working Registers

- Fully Static Operation

- Up to 16 MIPS Throughput at 16 MHz

- On-chip 2-cycle Multiplier

- High Endurance Non-volatile Memory segments

- 8K Bytes of In-System Self-programmable Flash program memory

- 512 Bytes EEPROM

- 1K Byte Internal SRAM

- Write/Erase Cycles: 10,000 Flash/100,000 EEPROM

- Data retention: 20 years at 85°C/100 years at 25°C<sup>(1)</sup>

- Optional Boot Code Section with Independent Lock Bits In-System Programming by On-chip Boot Program True Read-While-Write Operation

- Programming Lock for Software Security

- Peripheral Features

- Two 8-bit Timer/Counters with Separate Prescaler, one Compare Mode

- One 16-bit Timer/Counter with Separate Prescaler, Compare Mode, and Capture Mode

- Real Time Counter with Separate Oscillator

- Three PWM Channels

- 8-channel ADC in TQFP and QFN/MLF package Eight Channels 10-bit Accuracy

- 6-channel ADC in PDIP package Six Channels 10-bit Accuracy

- Byte-oriented Two-wire Serial Interface

- Programmable Serial USART

- Master/Slave SPI Serial Interface

- Programmable Watchdog Timer with Separate On-chip Oscillator

- On-chip Analog Comparator

- Special Microcontroller Features

- Power-on Reset and Programmable Brown-out Detection

- Internal Calibrated RC Oscillator

- External and Internal Interrupt Sources

- Five Sleep Modes: Idle, ADC Noise Reduction, Power-save, Power-down, and

- Standby

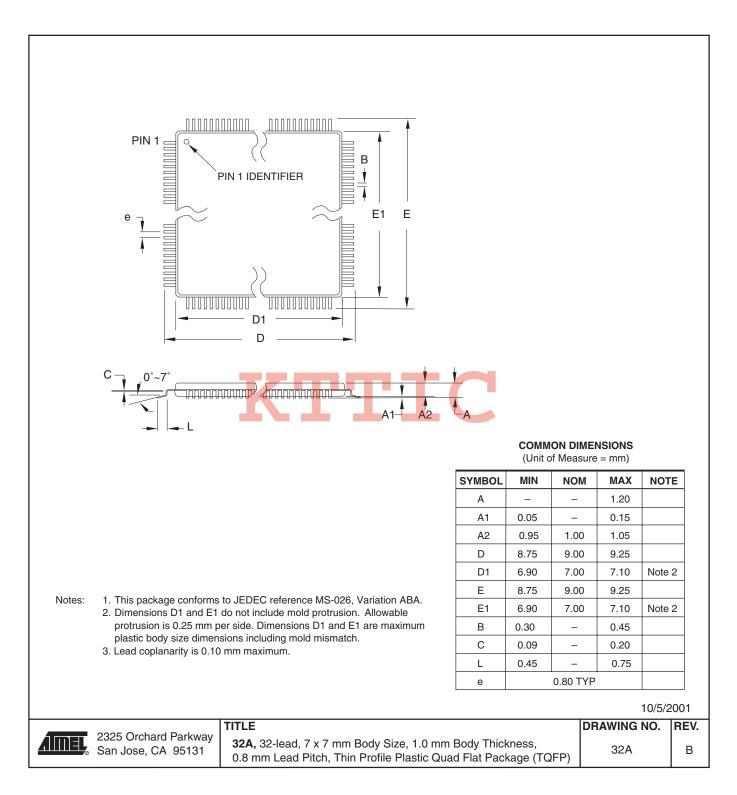

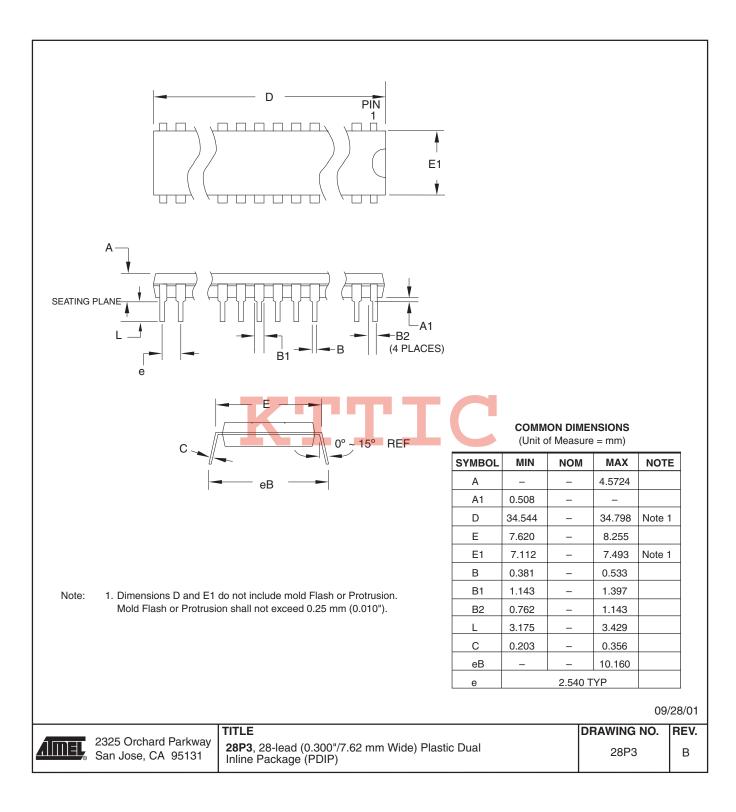

- I/O and Packages

- 23 Programmable I/O Lines

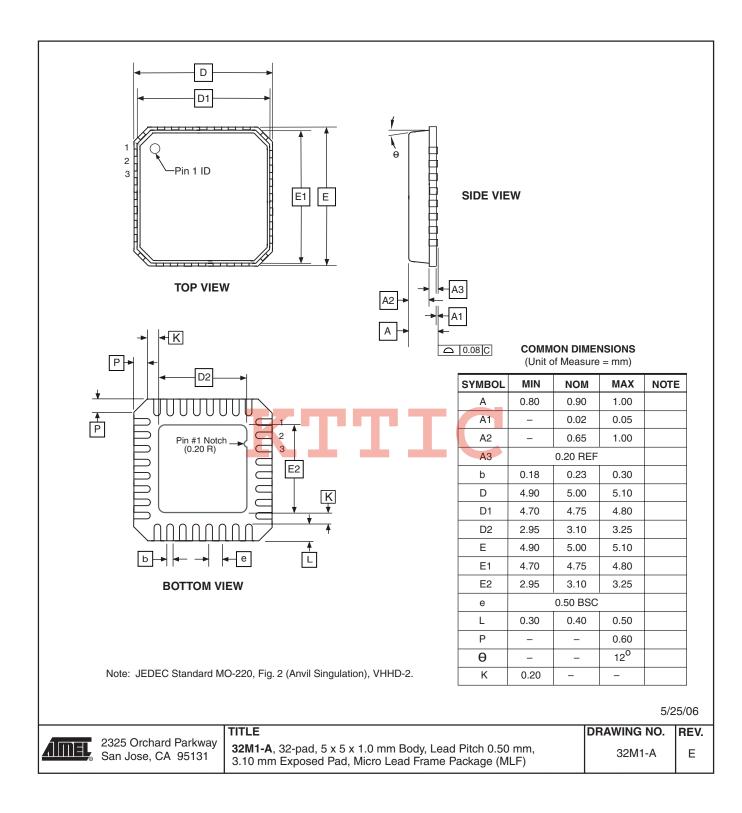

- 28-lead PDIP, 32-lead TQFP, and 32-pad QFN/MLF

- Operating Voltages

- 2.7 5.5V (ATmega8L)

- 4.5 5.5V (ATmega8)

- Speed Grades

- 0 8 MHz (ATmega8L)

- 0 16 MHz (ATmega8)

- Power Consumption at 4 Mhz, 3V, 25°C

- Active: 3.6 mA

- Idle Mode: 1.0 mA

- Power-down Mode: 0.5 μA

8-bit **AVR**<sup>®</sup> with 8K Bytes In-System Programmable Flash

ATmega8 ATmega8L

### Summary

http://www.kttic.com

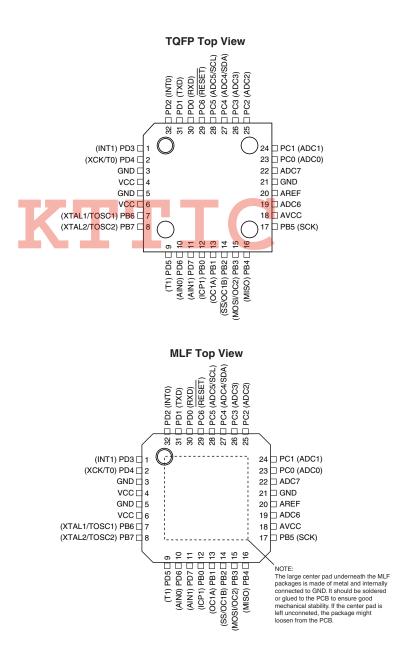

### Pin Configurations

|                   | FDIF |    |                  |

|-------------------|------|----|------------------|

|                   |      |    |                  |

| (RESET) PC6       | 1    | 28 | PC5 (ADC5/SCL)   |

| (RXD) PD0 🗆       | 2    | 27 | □ PC4 (ADC4/SDA) |

| (TXD) PD1 🗆       | 3    | 26 | PC3 (ADC3)       |

| (INT0) PD2 🗆      | 4    | 25 | PC2 (ADC2)       |

| (INT1) PD3 🗆      | 5    | 24 | PC1 (ADC1)       |

| (XCK/T0) PD4 🗆    | 6    | 23 | PC0 (ADC0)       |

| VCC 🗆             | 7    | 22 | 🗆 GND            |

| GND 🗆             | 8    | 21 | □ AREF           |

| (XTAL1/TOSC1) PB6 | 9    | 20 | AVCC             |

| (XTAL2/TOSC2) PB7 | 10   | 19 | PB5 (SCK)        |

| (T1) PD5 🗆        | 11   | 18 | □ PB4 (MISO)     |

| (AIN0) PD6 🗆      | 12   | 17 | PB3 (MOSI/OC2)   |

| (AIN1) PD7 🗆      | 13   | 16 | PB2 (SS/OC1B)    |

| (ICP1) PB0 🗆      | 14   | 15 | PB1 (OC1A)       |

|                   |      |    |                  |

PDIP

<sup>2</sup> ATmega8(L)

### http://www.kttirs.wronon

### ATmega8(L)

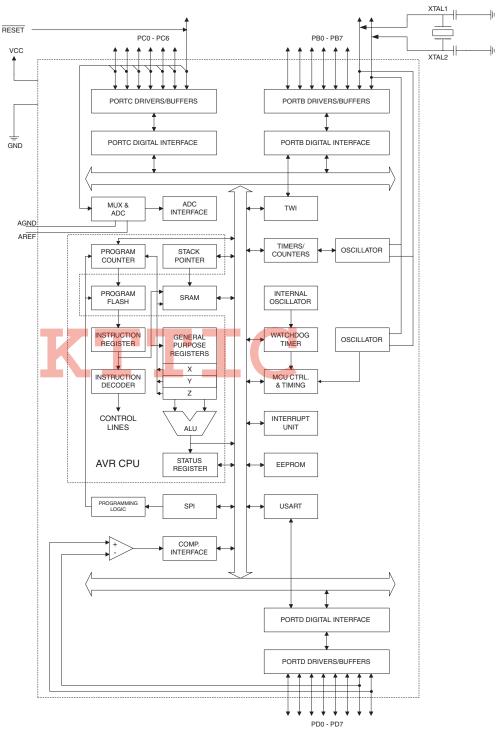

### **Overview**

The ATmega8 is a low-power CMOS 8-bit microcontroller based on the AVR RISC architecture. By executing powerful instructions in a single clock cycle, the ATmega8 achieves throughputs approaching 1 MIPS per MHz, allowing the system designer to optimize power consumption versus processing speed.

Block Diagram Figure 1. Block Diagram

The AVR core combines a rich instruction set with 32 general purpose working registers. All the 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle. The resulting architecture is more code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers.

The ATmega8 provides the following features: 8K bytes of In-System Programmable Flash with Read-While-Write capabilities, 512 bytes of EEPROM, 1K byte of SRAM, 23 general purpose I/O lines, 32 general purpose working registers, three flexible Timer/Counters with compare modes, internal and external interrupts, a serial programmable USART, a byte oriented Two-wire Serial Interface, a 6-channel ADC (eight channels in TQFP and QFN/MLF packages) with 10-bit accuracy, a programmable Watchdog Timer with Internal Oscillator, an SPI serial port, and five software selectable power saving modes. The Idle mode stops the CPU while allowing the SRAM, Timer/Counters, SPI port, and interrupt system to continue functioning. The Power-down mode saves the register contents but freezes the Oscillator, disabling all other chip functions until the next Interrupt or Hardware Reset. In Power-save mode, the asynchronous timer continues to run, allowing the user to maintain a timer base while the rest of the device is sleeping. The ADC Noise Reduction mode stops the CPU and all I/O modules except asynchronous timer and ADC, to minimize switching noise during ADC conversions. In Standby mode, the crystal/resonator Oscillator is running while the rest of the device is sleeping. This allows very fast start-up combined with low-power consumption.

The device is manufactured using Atmel's high density non-volatile memory technology. The Flash Program memory can be reprogrammed In-System through an SPI serial interface, by a conventional non-volatile memory programmer, or by an On-chip boot program running on the AVR core. The boot program can use any interface to download the application program in the Application Flash memory. Software in the Boot Flash Section will continue to run while the Application Flash Section is updated, providing true Read-While-Write operation. By combining an 8-bit RISC CPU with In-System Self-Programmable Flash on a monolithic chip, the Atmel ATmega8 is a powerful microcontroller that provides a highly-flexible and cost-effective solution to many embedded control applications.

The ATmega8 AVR is supported with a full suite of program and system development tools, including C compilers, macro assemblers, program debugger/simulators, In-Circuit Emulators, and evaluation kits.

**Disclaimer** Typical values contained in this datasheet are based on simulations and characterization of other AVR microcontrollers manufactured on the same process technology. Min and Max values will be available after the device is characterized.

http://www.kttic.com

### **Pin Descriptions**

| VCC                                            | Digital supply voltage.                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND                                            | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Port B (PB7PB0)<br>XTAL1/XTAL2/TOSC1/<br>TOSC2 | Port B is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port B output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port B pins that are externally pulled low will source current if the pull-up resistors are activated. The Port B pins are tri-stated when a reset condition becomes active, even if the clock is not running. |

|                                                | Depending on the clock selection fuse settings, PB6 can be used as input to the inverting Oscil-<br>lator amplifier and input to the internal clock operating circuit.                                                                                                                                                                                                                                                                    |

|                                                | Depending on the clock selection fuse settings, PB7 can be used as output from the inverting Oscillator amplifier.                                                                                                                                                                                                                                                                                                                        |

|                                                | If the Internal Calibrated RC Oscillator is used as chip clock source, PB76 is used as TOSC21 input for the Asynchronous Timer/Counter2 if the AS2 bit in ASSR is set.                                                                                                                                                                                                                                                                    |

|                                                | The various special features of Port B are elaborated in "Alternate Functions of Port B" on page 58 and "System Clock and Clock Options" on page 25.                                                                                                                                                                                                                                                                                      |

| Port C (PC5PC0)                                | Port C is an 7-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port C output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port C pins that are externally pulled low will source current if the pull-up resistors are activated. The Port C pins are tri-stated when a reset condition becomes active, even if the clock is not running. |

| PC6/RESET                                      | If the RSTDISBL Fuse is programmed, PC6 is used as an I/O pin. Note that the electrical char-<br>acteristics of PC6 differ from those of the other pins of Port C.                                                                                                                                                                                                                                                                        |

|                                                | If the RSTDISBL Fuse is unprogrammed, PC6 is used as a Reset input. A low level on this pin for longer than the minimum pulse length will generate a Reset, even if the clock is not running. The minimum pulse length is given in Table 15 on page 38. Shorter pulses are not guaranteed to generate a Reset.                                                                                                                            |

|                                                | The various special features of Port C are elaborated on page 61.                                                                                                                                                                                                                                                                                                                                                                         |

| Port D (PD7PD0)                                | Port D is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port D output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port D pins that are externally pulled low will source current if the pull-up resistors are activated. The Port D pins are tri-stated when a reset condition becomes active, even if the clock is not running. |

|                                                | Port D also serves the functions of various special features of the ATmega8 as listed on page 63.                                                                                                                                                                                                                                                                                                                                         |

| RESET                                          | Reset input. A low level on this pin for longer than the minimum pulse length will generate a reset, even if the clock is not running. The minimum pulse length is given in Table 15 on page 38. Shorter pulses are not guaranteed to generate a reset.                                                                                                                                                                                   |

| AV <sub>cc</sub>                            | $AV_{CC}$ is the supply voltage pin for the A/D Converter, Port C (30), and ADC (76). It should be externally connected to $V_{CC}$ , even if the ADC is not used. If the ADC is used, it should be connected to $V_{CC}$ through a low-pass filter. Note that Port C (54) use digital supply voltage, $V_{CC}$ . |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AREF                                        | AREF is the analog reference pin for the A/D Converter.                                                                                                                                                                                                                                                           |

| ADC76 (TQFP and<br>QFN/MLF Package<br>Only) | In the TQFP and QFN/MLF package, ADC76 serve as analog inputs to the A/D converter. These pins are powered from the analog supply and serve as 10-bit ADC channels.                                                                                                                                               |

| Resources | A comprehensive set of development tools, application notes and datasheets are available for |

|-----------|----------------------------------------------------------------------------------------------|

|           | download on http://www.atmel.com/avr.                                                        |

**Data Retention** Reliability Qualification results show that the projected data retention failure rate is much less than 1 PPM over 20 years at 85°C or 100 years at 25°C.

### **Register Summary**

|                                           | 1        | -      | 1      |          |                                   | 1                 | 1             | 1       | 1      |                  |

|-------------------------------------------|----------|--------|--------|----------|-----------------------------------|-------------------|---------------|---------|--------|------------------|

| Address                                   | Name     | Bit 7  | Bit 6  | Bit 5    | Bit 4                             | Bit 3             | Bit 2         | Bit 1   | Bit 0  | Page             |

| 0x3F (0x5F)                               | SREG     | I      | Т      | Н        | S                                 | V                 | Ν             | Z       | С      | 11               |

| 0x3E (0x5E)                               | SPH      | -      | -      | -        | -                                 | -                 | SP10          | SP9     | SP8    | 13               |

| 0x3D (0x5D)                               | SPL      | SP7    | SP6    | SP5      | SP4                               | SP3               | SP2           | SP1     | SP0    | 13               |

| 0x3C (0x5C)                               | Reserved |        |        |          |                                   |                   |               |         |        |                  |

| 0x3B (0x5B)                               | GICR     | INT1   | INT0   | -        | -                                 | -                 | -             | IVSEL   | IVCE   | 49, 67           |

| 0x3A (0x5A)                               | GIFR     | INTF1  | INTF0  | -        | -                                 | -                 | -             | -       | -      | 68               |

| 0x39 (0x59)                               | TIMSK    | OCIE2  | TOIE2  | TICIE1   | OCIE1A                            | OCIE1B            | TOIE1         | -       | TOIE0  | 72, 102, 122     |

| 0x38 (0x58)                               | TIFR     | OCF2   | TOV2   | ICF1     | OCF1A                             | OCF1B             | TOV1          | -       | TOV0   | 73, 102, 122     |

| 0x37 (0x57)                               | SPMCR    | SPMIE  | RWWSB  | -        | RWWSRE                            | BLBSET            | PGWRT         | PGERS   | SPMEN  | 213              |

| 0x36 (0x56)                               | TWCR     | TWINT  | TWEA   | TWSTA    | TWSTO                             | TWWC              | TWEN          | -       | TWIE   | 171              |

| 0x35 (0x55)                               | MCUCR    | SE     | SM2    | SM1      | SM0                               | ISC11             | ISC10         | ISC01   | ISC00  | 33, 66           |

| 0x34 (0x54)                               | MCUCSR   | -      | -      | -        | -                                 | WDRF              | BORF          | EXTRF   | PORF   | 41               |

| 0x33 (0x53)                               | TCCR0    | -      | -      | -        | -                                 | -                 | CS02          | CS01    | CS00   | 72               |

| 0x32 (0x52)                               | TCNT0    |        |        |          | Timer/Cou                         | inter0 (8 Bits)   |               |         |        | 72               |

| 0x31 (0x51)                               | OSCCAL   |        |        |          | Oscillator Cal                    | ibration Register |               |         |        | 31               |

| 0x30 (0x50)                               | SFIOR    | -      | -      | -        | -                                 | ACME              | PUD           | PSR2    | PSR10  | 58, 75, 123, 193 |

| 0x2F (0x4F)                               | TCCR1A   | COM1A1 | COM1A0 | COM1B1   | COM1B0                            | FOC1A             | FOC1B         | WGM11   | WGM10  | 96               |

| 0x2E (0x4E)                               | TCCR1B   | ICNC1  | ICES1  | -        | WGM13                             | WGM12             | CS12          | CS11    | CS10   | 100              |

| 0x2D (0x4D)                               | TCNT1H   |        |        | Tim      | er/Counter1 – Co                  | unter Register Hi | gh byte       |         |        | 101              |

| 0x2C (0x4C)                               | TCNT1L   |        |        | Tim      | er/Counter1 – Co                  | unter Register Lo | ow byte       |         |        | 101              |

| 0x2B (0x4B)                               | OCR1AH   |        |        | Timer/Co | unter1 – Output C                 | Compare Register  | r A High byte |         |        | 101              |

| 0x2A (0x4A)                               | OCR1AL   |        |        | Timer/Co | ounter1 – Output 0                | Compare Registe   | r A Low byte  |         |        | 101              |

| 0x29 (0x49)                               | OCR1BH   |        |        | Timer/Co | unter1 – Output C                 | Compare Register  | B High byte   |         |        | 101              |

| 0x28 (0x48)                               | OCR1BL   |        |        | Timer/Co | ounter1 – Output 0                | Compare Registe   | r B Low byte  |         |        | 101              |

| 0x27 (0x47)                               | ICR1H    |        |        | Timer/   | Counter1 – Input                  | Capture Register  | High byte     |         |        | 102              |

| 0x26 (0x46)                               | ICR1L    |        |        | Timer/   | Counter1 – Input                  | Capture Register  | Low byte      |         |        | 102              |

| 0x25 (0x45)                               | TCCR2    | FOC2   | WGM20  | COM21    | COM20                             | WGM21             | CS22          | CS21    | CS20   | 117              |

| 0x24 (0x44)                               | TCNT2    |        |        |          | Timer/Cou                         | inter2 (8 Bits)   |               |         |        | 119              |

| 0x23 (0x43)                               | OCR2     |        |        | Ti       | mer/Counter2 Ou                   | tput Compare Re   | gister        |         |        | 119              |

| 0x22 (0x42)                               | ASSR     | -      | -      | _        | _                                 | AS2               | TCN2UB        | OCR2UB  | TCR2UB | 119              |

| 0x21 (0x41)                               | WDTCR    | -      | -      |          | WDCE                              | WDE               | WDP2          | WDP1    | WDP0   | 43               |

| 0x20 <sup>(1)</sup> (0x40) <sup>(1)</sup> | UBRRH    | URSEL  | -      | _        | -                                 |                   | UBR           | R[11:8] |        | 158              |

| 0x20(** (0x40)(**                         | UCSRC    | URSEL  | UMSEL  | UPM1     | UPM0                              | USBS              | UCSZ1         | UCSZ0   | UCPOL  | 156              |

| 0x1F (0x3F)                               | EEARH    | -      | _      |          | -                                 | -                 |               | -       | EEAR8  | 20               |

| 0x1E (0x3E)                               | EEARL    | EEAR7  | EEAR6  | EEAR5    | EEAR4                             | EEAR3             | EEAR2         | EEAR1   | EEAR0  | 20               |

| 0x1D (0x3D)                               | EEDR     |        |        |          | EEPROM                            | Data Register     |               |         |        | 20               |

| 0x1C (0x3C)                               | EECR     | -      | -      | -        | -                                 | EERIE             | EEMWE         | EEWE    | EERE   | 20               |

| 0x1B (0x3B)                               | Reserved |        |        |          |                                   |                   |               |         |        |                  |

| 0x1A (0x3A)                               | Reserved |        |        |          |                                   |                   |               |         |        |                  |

| 0x19 (0x39)                               | Reserved |        |        |          |                                   |                   |               |         |        |                  |

| 0x18 (0x38)                               | PORTB    | PORTB7 | PORTB6 | PORTB5   | PORTB4                            | PORTB3            | PORTB2        | PORTB1  | PORTB0 | 65               |

| 0x17 (0x37)                               | DDRB     | DDB7   | DDB6   | DDB5     | DDB4                              | DDB3              | DDB2          | DDB1    | DDB0   | 65               |

| 0x16 (0x36)                               | PINB     | PINB7  | PINB6  | PINB5    | PINB4                             | PINB3             | PINB2         | PINB1   | PINB0  | 65               |

| 0x15 (0x35)                               | PORTC    | -      | PORTC6 | PORTC5   | PORTC4                            | PORTC3            | PORTC2        | PORTC1  | PORTC0 | 65               |

| 0x14 (0x34)                               | DDRC     | -      | DDC6   | DDC5     | DDC4                              | DDC3              | DDC2          | DDC1    | DDC0   | 65               |

| 0x13 (0x33)                               | PINC     | -      | PINC6  | PINC5    | PINC4                             | PINC3             | PINC2         | PINC1   | PINC0  | 65               |

| 0x12 (0x32)                               | PORTD    | PORTD7 | PORTD6 | PORTD5   | PORTD4                            | PORTD3            | PORTD2        | PORTD1  | PORTD0 | 65               |

| 0x11 (0x31)                               | DDRD     | DDD7   | DDD6   | DDD5     | DDD4                              | DDD3              | DDD2          | DDD1    | DDD0   | 65               |

| 0x10 (0x30)                               | PIND     | PIND7  | PIND6  | PIND5    | PIND4                             | PIND3             | PIND2         | PIND1   | PIND0  | 65               |

| 0x0F (0x2F)                               | SPDR     |        |        |          | SPI Da                            | ta Register       |               |         |        | 131              |

| 0x0E (0x2E)                               | SPSR     | SPIF   | WCOL   | -        | -                                 | -                 | -             | -       | SPI2X  | 131              |

| 0x0D (0x2D)                               | SPCR     | SPIE   | SPE    | DORD     | MSTR                              | CPOL              | CPHA          | SPR1    | SPR0   | 129              |

| 0x0C (0x2C)                               | UDR      |        |        |          | USART I/O                         | Data Register     | . <u> </u>    |         |        | 153              |

| 0x0B (0x2B)                               | UCSRA    | RXC    | TXC    | UDRE     | FE                                | DOR               | PE            | U2X     | MPCM   | 154              |

| 0x0A (0x2A)                               | UCSRB    | RXCIE  | TXCIE  | UDRIE    | RXEN                              | TXEN              | UCSZ2         | RXB8    | TXB8   | 155              |

| 0x09 (0x29)                               | UBRRL    |        |        |          | USART Baud Ra                     | te Register Low b | oyte          |         |        | 158              |

| 0x08 (0x28)                               | ACSR     | ACD    | ACBG   | ACO      | ACI                               | ACIE              | ACIC          | ACIS1   | ACIS0  | 194              |

| 0x07 (0x27)                               | ADMUX    | REFS1  | REFS0  | ADLAR    | _                                 | MUX3              | MUX2          | MUX1    | MUX0   | 205              |

| 0x06 (0x26)                               | ADCSRA   | ADEN   | ADSC   | ADFR     | ADIF                              | ADIE              | ADPS2         | ADPS1   | ADPS0  | 207              |

|                                           | ADCH     |        |        |          | ADC Data Re                       | egister High byte |               |         |        | 208              |

| 0x05 (0x25)                               | ADOIT    |        |        |          |                                   |                   |               |         |        |                  |

| 0x05 (0x25)<br>0x04 (0x24)                | ADCL     |        |        |          | ADC Data Re                       | egister Low byte  |               |         |        | 208              |

|                                           |          |        |        | 1        | ADC Data Re<br>Two-wire Serial In |                   | ister         |         |        | 208<br>173       |

**Register Summary (Continued)**

#### Address Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Page TWSR TWS6 TWS5 TWS4 TWS3 TWPS1 TWPS0 0x01 (0x21) TWS7 173 0x00 (0x20) TWBR Two-wire Serial Interface Bit Rate Register 171

Notes:

1. Refer to the USART description for details on how to access UBRRH and UCSRC. 2. For compatibility with future devices, reserved bits should be written to zero if accessed. Reserved I/O memory addresses

should never be written. 3. Some of the Status Flags are cleared by writing a logical one to them. Note that the CBI and SBI instructions will operate on all bits in the I/O Register, writing a one back into any flag read as set, thus clearing the flag. The CBI and SBI instructions work with registers 0x00 to 0x1F only.

### **Instruction Set Summary**

| Mnemonics        | Operands         | Description                              | Operation                                                                                | Flags          | #Clocks |

|------------------|------------------|------------------------------------------|------------------------------------------------------------------------------------------|----------------|---------|

| ARITHMETIC AND L | OGIC INSTRUCTION | Ş                                        | -                                                                                        |                | -       |

| ADD              | Rd, Rr           | Add two Registers                        | $Rd \leftarrow Rd + Rr$                                                                  | Z,C,N,V,H      | 1       |

| ADC              | Rd, Rr           | Add with Carry two Registers             | $Rd \leftarrow Rd + Rr + C$                                                              | Z,C,N,V,H      | 1       |

| ADIW             | Rdl,K            | Add Immediate to Word                    | $Rdh:RdI \leftarrow Rdh:RdI + K$                                                         | Z,C,N,V,S      | 2       |

| SUB              | Rd, Rr           | Subtract two Registers                   | Rd ← Rd - Rr                                                                             | Z,C,N,V,H      | 1       |

| SUBI             | Rd, K            | Subtract Constant from Register          | $Rd \leftarrow Rd - K$                                                                   | Z,C,N,V,H      | 1       |

| SBC              | Rd, Rr           | Subtract with Carry two Registers        | $Rd \leftarrow Rd - Rr - C$                                                              | Z,C,N,V,H      | 1       |

| SBCI             | Rd, K            | Subtract with Carry Constant from Reg.   | $Rd \gets Rd - K - C$                                                                    | Z,C,N,V,H      | 1       |

| SBIW             | Rdl,K            | Subtract Immediate from Word             | $Rdh:Rdl \leftarrow Rdh:Rdl - K$                                                         | Z,C,N,V,S      | 2       |

| AND              | Rd, Rr           | Logical AND Registers                    | $Rd \leftarrow Rd \bullet Rr$                                                            | Z,N,V          | 1       |

| ANDI             | Rd, K            | Logical AND Register and Constant        | $Rd \leftarrow Rd \bullet K$                                                             | Z,N,V          | 1       |

| OR               | Rd, Rr           | Logical OR Registers                     | $Rd \leftarrow Rd v Rr$                                                                  | Z,N,V          | 1       |

| ORI              | Rd, K            | Logical OR Register and Constant         | $Rd \leftarrow Rd \vee K$                                                                | Z,N,V          | 1       |

| EOR              | Rd, Rr           | Exclusive OR Registers                   | $Rd \leftarrow Rd \oplus Rr$                                                             | Z,N,V          | 1       |

| COM              | Rd               | One's Complement                         | $Rd \leftarrow 0xFF - Rd$                                                                | Z,C,N,V        | 1       |

| NEG              | Rd               | Two's Complement                         | Rd ← 0x00 – Rd                                                                           | Z,C,N,V,H      | 1       |

| SBR              | Rd,K             | Set Bit(s) in Register                   | Rd ← Rd v K                                                                              | Z,N,V          | 1       |

| CBR              | Rd,K             | Clear Bit(s) in Register                 | $Rd \leftarrow Rd \bullet (0xFF - K)$                                                    | Z,N,V          | 1       |

| INC              | Rd               | Increment                                | $Rd \leftarrow Rd + 1$                                                                   | Z,N,V          | 1       |

| DEC              | Rd               | Decrement                                | $Rd \leftarrow Rd - 1$                                                                   | Z,N,V<br>Z,N,V | 1       |

| TST              | Rd               | Test for Zero or Minus                   | $Ra \leftarrow Ra - 1$<br>$Rd \leftarrow Rd \bullet Rd$                                  | Z,N,V<br>Z,N,V | 1       |

|                  |                  |                                          |                                                                                          |                |         |

| CLR              | Rd               | Clear Register                           | $Rd \leftarrow Rd \oplus Rd$                                                             | Z,N,V          | 1       |

| SER              | Rd               | Set Register                             | Rd ← 0xFF                                                                                | None           | 1       |

| MUL              | Rd, Rr           | Multiply Unsigned                        | $R1:R0 \leftarrow Rd \times Rr$                                                          | Z,C            | 2       |

| MULS             | Rd, Rr           | Multiply Signed                          | $R1:R0 \leftarrow Rd \times Rr$                                                          | Z,C            | 2       |

| MULSU            | Rd, Rr           | Multiply Signed with Unsigned            | $R1:R0 \leftarrow Rd \times Rr$                                                          | Z,C            | 2       |

| FMUL             | Rd, Rr           | Fractional Multiply Unsigned             | $R1:R0 \leftarrow (Rd \times Rr) << 1$                                                   | Z,C            | 2       |

| FMULS            | Rd, Rr           | Fractional Multiply Signed               | $R1:R0 \leftarrow (Rd \times Rr) << 1$                                                   | Z,C            | 2       |

| FMULSU           | Rd, Rr           | Fractional Multiply Signed with Unsigned | $R1:R0 \leftarrow (Rd \times Rr) \le 1$                                                  | Z,C            | 2       |

| BRANCH INSTRUC   | TIONS            |                                          |                                                                                          | - 1            | 1       |

| RJMP             | k                | Relative Jump                            | $PC \leftarrow PC + k + 1$                                                               | None           | 2       |

| IJMP             |                  | Indirect Jump to (Z)                     | PC ← Z                                                                                   | None           | 2       |

| RCALL            | k                | Relative Subroutine Call                 | $PC \leftarrow PC + k + 1$                                                               | None           | 3       |

| ICALL            |                  | Indirect Call to (Z)                     | PC ← Z                                                                                   | None           | 3       |

| RET              |                  | Subroutine Return                        | $PC \leftarrow STACK$                                                                    | None           | 4       |

| RETI             |                  | Interrupt Return                         | $PC \leftarrow STACK$                                                                    | 1              | 4       |

| CPSE             | Rd,Rr            | Compare, Skip if Equal                   | if (Rd = Rr) PC $\leftarrow$ PC + 2 or 3                                                 | None           | 1/2/3   |

| CP               | Rd,Rr            | Compare                                  | Rd – Rr                                                                                  | Z, N,V,C,H     | 1       |

| CPC              | Rd,Rr            | Compare with Carry                       | Rd – Rr – C                                                                              | Z, N,V,C,H     | 1       |

| CPI              | Rd,K             | Compare Register with Immediate          | Rd – K                                                                                   | Z, N,V,C,H     | 1       |

| SBRC             | Rr, b            | Skip if Bit in Register Cleared          | if $(Rr(b)=0) PC \leftarrow PC + 2 \text{ or } 3$                                        | None           | 1/2/3   |

| SBRS             | Rr, b            | Skip if Bit in Register is Set           | if (Rr(b)=1) PC $\leftarrow$ PC + 2 or 3                                                 | None           | 1/2/3   |

| SBIC             | P, b             | Skip if Bit in I/O Register Cleared      | if $(P(b)=0) PC \leftarrow PC + 2 \text{ or } 3$                                         | None           | 1/2/3   |

| SBIS             | P, b             | Skip if Bit in I/O Register is Set       | if $(P(b)=1) PC \leftarrow PC + 2 \text{ or } 3$                                         | None           | 1/2/3   |

| BRBS             | s, k             | Branch if Status Flag Set                | if (SREG(s) = 1) then $PC \leftarrow PC+k + 1$                                           | None           | 1/2     |

| BRBC             | s, k             | Branch if Status Flag Cleared            | if $(SREG(s) = 0)$ then $PC \leftarrow PC+k + 1$                                         | None           | 1/2     |

| BREQ             | k k              | Branch if Equal                          | if $(Z = 1)$ then PC $\leftarrow$ PC + k + 1                                             | None           | 1/2     |

| BRNE             | k                | Branch if Not Equal                      | if (Z = 0) then PC $\leftarrow$ PC + k + 1<br>if (Z = 0) then PC $\leftarrow$ PC + k + 1 | None           | 1/2     |

| BRCS             | k k              | Branch if Carry Set                      | if (C = 1) then PC $\leftarrow$ PC + k + 1<br>if (C = 1) then PC $\leftarrow$ PC + k + 1 |                |         |

|                  |                  |                                          |                                                                                          | None           | 1/2     |

| BRCC             | k                | Branch if Carry Cleared                  | if $(C = 0)$ then PC $\leftarrow$ PC + k + 1                                             | None           | 1/2     |

| BRSH             | k                | Branch if Same or Higher                 | if (C = 0) then PC $\leftarrow$ PC + k + 1                                               | None           | 1/2     |

| BRLO             | k                | Branch if Lower                          | if (C = 1) then PC $\leftarrow$ PC + k + 1                                               | None           | 1/2     |

| BRMI             | k                | Branch if Minus                          | if $(N = 1)$ then PC $\leftarrow$ PC + k + 1                                             | None           | 1/2     |

| BRPL             | k                | Branch if Plus                           | if $(N = 0)$ then PC $\leftarrow$ PC + k + 1                                             | None           | 1/2     |

| BRGE             | k                | Branch if Greater or Equal, Signed       | if (N $\oplus$ V= 0) then PC $\leftarrow$ PC + k + 1                                     | None           | 1/2     |

| BRLT             | k                | Branch if Less Than Zero, Signed         | if (N $\oplus$ V= 1) then PC $\leftarrow$ PC + k + 1                                     | None           | 1/2     |

| BRHS             | k                | Branch if Half Carry Flag Set            | if (H = 1) then PC $\leftarrow$ PC + k + 1                                               | None           | 1/2     |

| BRHC             | k                | Branch if Half Carry Flag Cleared        | if (H = 0) then PC $\leftarrow$ PC + k + 1                                               | None           | 1/2     |

| BRTS             | k                | Branch if T Flag Set                     | if (T = 1) then PC $\leftarrow$ PC + k + 1                                               | None           | 1/2     |

| BRTC             | k                | Branch if T Flag Cleared                 | if (T = 0) then PC $\leftarrow$ PC + k + 1                                               | None           | 1/2     |

| BRVS             | k                | Branch if Overflow Flag is Set           | if (V = 1) then PC $\leftarrow$ PC + k + 1                                               | None           | 1/2     |

| DIVUS            |                  |                                          |                                                                                          |                |         |

| BRVC             | k                | Branch if Overflow Flag is Cleared       | if (V = 0) then PC $\leftarrow$ PC + k + 1                                               | None           | 1/2     |

### Instruction Set Summary (Continued)

| BND         *         Branch Interrupt Disability         # (1 = 0 pm R ) = - P = + + 1         None           DATA TANASSER TRAVEOROS         Ref. FX         Move Benzee Registers.         Ref. FX         Nore         Nore           MOV         Ref. FX         Load Internative Move Benzee Registers.         Ref. FX         Nore         Nore           L01         Ref. X         Load Internative Move Benzee         Ref. FX         Nore           L01         Ref. X         Load Internative Move Benzee         Ref. FX         Nore           L0         Ref. X         Load Internative Move Benzee         FX         Nore           L0         Ref. Y         Load Internative Move Benzee         FX         Nore           L0         Ref. Y         Load Internative Move Benzee         FX         Nore           L0         Ref. Y         Load Internative Move Benzee         FX         Nore           L0         Ref. Y         Load Internative Move Benzee         FX         Nore           L0         Ref. Y         Load Internative Move Benzee         FX         Nore           L0         Ref. Y         Sover Internative Move Benzee         FX         Nore           L0         Ref. Y         Sover Internative Move Benzee         F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | BRIE          | k           | Branch if Interrupt Enabled      | if (I = 1) then PC $\leftarrow$ PC + k + 1  | None    | 1/2     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------|----------------------------------|---------------------------------------------|---------|---------|

| MOV         R.J. R.         Nove Source Registers         R0 + R1         Nove           MOVM         R.J. R.         Copy Register Word         Ret + K1         Nove           LDI         R.J. K.         Last Indires         Ret + K1         Nove           LDI         R.J. K.         Last Indires         Ret + C0         Nove           LD         R.J. X.         Last Indires         Ret + C0         Nove           LD         R.J. X.         Last Indires and Position.         Ret - (Y) + V + 1         Nove           LD         R.J. V.         Last Indires and Position.         Ret - (Y) = (Y + V + 1)         Nove           LD         R.J. V.         Last Indires and Position.         Ret - (Y) = (Y + V + 1)         Nove           LD         R.J. V.         Last Indires and Position.         Ret - (Y) = (Y + V + 1)         Nove           LD         Last Indires and Position.         Ret - (Z) = (Z + 1)         Nove         Nove           LD         Last Indires and Position.         Ret - (Z) = (Z + 1)         Nove           LD         Last Indires and Position.         Ret - (Z) = (Z + 1)         Nove           LD         Last Indires and Position.         Ret - (Z) = (Z + 1)         Nove           LD         Last I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | BRID          | k           | Branch if Interrupt Disabled     | if ( I = 0) then PC $\leftarrow$ PC + k + 1 | None    | 1/2     |

| MOW         R.A. K.         Cog/ Regiser Wood         Red + K.         None           LDI         Rd, K.         Load Indication         Rd + CQ         None           LD         Rd, X.         Load Indication         Rd + CQ         None           LD         Rd, X.         Load Indicat and ProCes.         Rd + CQ         None           LD         Rd, Y.         Load Indication ProCes.         X + X + 1. Rd + CQ         None           LD         Rd Y.         Load Indication ProCes.         Y + Y + 7. Rd + CY         None           LD         Rd Y.         Load Indication ProCes.         Y + Y + 7. Rd + CY         None           LD         Rd Y.         Load Indication ProCes.         Y + Y + 7. Rd + CY         None           LD         Rd Z.         Load Indication ProCes.         Y + Y + 7. Rd + CY         None           LD         Rd Z.         Load Indication ProCes.         Y + Y + 7. Rd + CZ         None           LD         Rd Z.         Load Indication ProCes.         Y + Y + 7. Rd + CZ         None           LD         Rd Z.         Load Indication ProCes.         Y + Y + 7. Rd + CZ         None           LD         Rd Z.         Load Indication ProCes.         Y + Y + Y + Y + Y + Y + Y + Y + Y + Y +                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | DATA TRANSFER | NSTRUCTIONS |                                  |                                             |         |         |

| Lb1         R±, K         Land Indian         R± + C         Nome           LD         R±, X         Land Indian and Post-Inc.         R± + C(x), X + X + 1         Nome           LD         R±, X         Land Indian and Post-Inc.         R± + C(x), X + X + 1         Nome           LD         R±, X         Land Indian and Post-Inc.         R± + (Y), X + Y + 1         Nome           LD         R±, Y         Land Indian and Post-Inc.         R± + (Y) + (Y + Y + 1)         Nome           LD         R±, Y         Land Indian and Post-Inc.         R± + (Y)         Nome           LD         R±, Y         Land Indian and Post-Inc.         R± + (Z)         Nome           LD         R±, Z         Land Indian and Post-Inc.         R± + (Z)         Nome           LD         R±, Z         Land Indian and Post-Inc.         R± + (Z)         Nome           LD         R±, Z         Land Indian and Post-Inc.         R± + (Z)         Nome           LD         R±, Z         Land Indian and Post-Inc.         R± + (Z)         Nome           LD         R± = (Z)         Nome         Nome         Nome           LD         Land Indian and Post-Inc.         X + X + 1, R± N         Nome           LD         Land Indigent and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | MOV           | Rd, Rr      | Move Between Registers           | $Rd \leftarrow Rr$                          | None    | 1       |

| LDRd. ×Land Indicar of Polin.Rd + (D)NumeLDRd. ×Land Indicar of Polin.Rd + (D)NumeLDRd. ×Land Indicar of Polin.X + × 1, Rd + (D)NumeLDRd. ×Land Indicar of Polin.Rd + (T)NumeLDRd. ×Land Indicar of Polin.Rd + (T)NumeLDRd. ×Land Indicar of Polin.Rd + (T) + 1NumeLDRd. ×Land Indicar of Polin.Rd + (T) + 0NumeLDRd. ×Land Indicar of Polin.Rd + (T) + 0NumeLDRd. ×Land Indicar of Polin.Rd + (Z) 2 - 2.11NumeLDRd. ×Land Indicar of Polin.Rd + (Z) 2 - 2.11NumeLDRd. ×Land Indicar of Polin.Rd + (Z) 2 - 2.11NumeLDRd. ×Land Indicar of Polin.Rd + (Z) 2 - 2.11NumeLDRd. ×Land Indicar of Polin.Rd + (Z) 2 - 2.11NumeSTX, RTStam Indicar of Polin.(D) + R, × + 1.1NumeSTX, RTStam Indicar of Polin.(D) + R, × + 1.1NumeSTX, RTStam Indicar of Polin.(D) + R, × + 1.1NumeSTX, RTStam Indicar of Polin.(D) + R, × + 1.1NumeSTX, RTStam Indicar of Polin.(D) + R, × + 1.1NumeSTX, RTStam Indicar of Polin.(D) + R, × + 1.1NumeSTX, RTStam Indicar of Polin.(D) + R, × + 1.1NumeST<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | MOVW          | Rd, Rr      | Copy Register Word               | $Rd+1:Rd \leftarrow Rr+1:Rr$                | None    | 1       |

| LD         RdX         Load Indiget and Pre-Boc.         Rd - (X), K - X + 1         None           LD         Rd, Y         Load Indiget and Pre-Boc.         X + X + 1, Rd + (D)         None           LD         Rd, Y         Load Indiget and Pre-Boc.         Y + Y + 1, Rd + (P)         None           LD         Rd, Y         Load Indiget and Pre-Boc.         Y + Y + 1, Rd + (P)         None           LD         Rd, Y         Load Indiget and Pre-Boc.         Y + Y + 1, Rd + (P)         None           LD         Rd, Z         Load Indiget and Pre-Boc.         Z + Z + 1, Rd + (P)         None           LD         Rd, Z         Load Indiget and Pre-Boc.         Z + Z + 1, Rd + (P)         None           LD         Rd, Z         Load Indiget and Pre-Boc.         Z + Z + 1, Rd + (P)         None           LD         Rd, Z         Load Indiget and Pre-Boc.         Z + Z + 1, Rd + (P)         None           ST         X, Rr         Store Indiget and Pre-Boc.         X + X + (X + 1)         None           ST         X, Rr         Store Indiget and Pre-Boc.         X + X + (Y + 1)         None           ST         X, Rr         Store Indiget and Pre-Boc.         X + X + (Y + 1)         None           ST         Y, Rr         Store Indinget and Pr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | LDI           | Rd, K       | Load Immediate                   | $Rd \leftarrow K$                           | None    | 1       |

| LD         Rd, Y         Load Indired are Pro-Dec.         X ← X + 1, Rd ← (Y),         Nome           LD         Rd, Y         Load Indired are Pro-Dec.         Rd ← (Y), Y ← Y + 1,         Nome           LD         Rd, Y         Load Indired are Pro-Dec.         Y ← Y + 1, Rd ← (Y),         Nome           LDD         Rd, Y         Load Indired are Pro-Dec.         Y ← Y + 1, Rd ← (Y),         Nome           LD         Rd, Z         Load Indired are Pro-Dec.         Z + ∠ + 1, Rd ← (Z),         Nome           LD         Rd, Z         Load Indired are Pro-Dec.         Z + ∠ + 1, Rd ← (Z),         Nome           LD         Rd, Z         Load Indired are Pro-Dec.         Z + ∠ + 1, Rd ← (Z),         Nome           LDS         Rd, X         Load Dreed from SMAM         Rd + (Z + q)         Nome           ST         X, Rr         Store Indired and Pro-Dec.         Z + Z + 1, Rd + (Z, Z + 1)         Nome           ST         X, Rr         Store Indired and Pro-Dec.         (Y + K + X + 1, R)         Nome           ST         X, Rr         Store Indired and Pro-Dec.         (Y + K + 1, (Y) + Fr.         Nome           ST         X, Rr         Store Indired and Pro-Dec.         (Y + K + 1, (Y) + Fr.         Nome           ST         X, Rr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |               |             |                                  |                                             | None    | 2       |

| LD         Rd, Y         Load Indiget and Peeche.         Rd + (Y)         None           LD         Rd, Y         Load Indiget and Peeche.         Y + Y, 1, Rd + (Y)         None           LD         Rd, Y         Load Indiget and Peeche.         Rd + (Q)         None           LD         Rd, Z         Load Indiget and Peeche.         Rd + (Q)         None           LD         Rd, Z         Load Indiget and Peeche.         Rd + (Q)         None           LD         Rd, Z         Load Indiget and Peeche.         Rd + (Q)         None           LD         Rd, Z         Load Indiget and Peeche.         Rd + (Q)         None           LDS         Rd, R         Load Indiget and Peeche.         Rd + (Q)         None           ST         X, Rr         Store Indiget and Peoche.         Y+ (X)         None           ST         X, Rr         Store Indiget and Peoche.         Y+ Y+ 1, (Y) + Rr         None           ST         Y, Rr         Store Indiget and Peoche.         Y+ Y+ 1, (Y) + Rr         None           ST         Y, Rr         Store Indiget and Peoche.         Y+ Y+ 1, (Y) + Rr         None           ST         Y, Rr         Store Indiget and Peoche.         Y+ Y+ 1, (Y) + Rr         None           <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |               |             | Load Indirect and Post-Inc.      |                                             | None    | 2       |

| LD         Rd. Y         Load Indiana and PeoDec.         Rd. + (Y, Y - Y + 1)         None           LDD         Rd. Y         Load Indiana with Displacement         Rd + (Y, q)         None           LDD         Rd. Z         Load Indiana with Displacement         Rd + (Y, q)         None           LD         Rd. Z         Load Indiana and PeoDec.         Rd + (Z, Z + Z+1)         None           LD         Rd. Z         Load Indiana and PeoDec.         Z + Z + 1, Rd + (Q)         None           LDS         Rd. X         Load Indiana and PeoDec.         Z + Z + 1, Rd + (Q)         None           LDS         Rd. X         Load Orient from SAM         Rd + (X + Q)         None           ST         X, Rr         Store Indiana and PeoDec.         X + X + 1, (X) + Rr         None           ST         X, Rr         Store Indiana and PeoDec.         (Y + X + X + 1)         None           ST         X, Rr         Store Indiana and PeoDec.         (Y + K + Y + 1)         None           ST         X, Rr         Store Indiana and PeoDec.         (Y + X + Y + Y + 1)         None           ST         X, Rr         Store Indiana and PeoDec.         (Y + X + Y + Y + 1)         None           ST         X, Rr         Store Indiana and PeoDec.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |               |             |                                  |                                             |         | 2       |

| LD         Rs/Y-q         Load Indust and Pa-bac.         Y - Y - 1, Rd - (Y) - (Y)         None           LD         Rs/Y-q         Load Indust with Deplayment         Rd + (Z)         None           LD         Rs/Z         Load Indust and Po-sho.         Rd + (Z)         None           LD         Rs/Z         Load Indust and Po-sho.         Rd + (Z)         None           LD         Rs/Z         Load Indust and Po-sho.         Rd + (Z)         None           LD         Rs/Z         Load Indust and Po-sho.         Rd + (Z)         None           LDS         Rs/K         Load Indust and Po-sho.         Rd + (Z)         None           LDS         Rs/K         Stree Induct and Po-sho.         (Y) + R'         None           ST         X, R'         Stree Induct and Po-sho.         (Y) + R'         None           ST         X, R'         Stree Induct and Po-sho.         (Y) + R'         None           ST         X, R'         Stree Induct and Po-sho.         (Y + R')         None           ST         X, R'         Stree Induct and Po-sho.         (Y + R')         None           ST         X, R'         Stree Induct and Po-sho.         (Y + R')         None           ST         Z, R'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |               |             |                                  |                                             |         | 2       |

| LDD $Bd_r / r_q$ Load Indiance with Desponsement $Bd_r - (2, r)$ NomeLD $Bd_r / 2$ Load Indiance and Post-bac. $Bd_r - (2)_r / - r / r / q)$ NomeLD $Bd_r / 2$ Load Indiance and Post-bac. $Z - r - 1, Bd_r - (2)_r / q)$ NomeLD $Bd_r / 2$ Load Indiance and Post-bac. $Z - r - 1, Bd_r - (2)_r / q)$ NomeLDD $Bd_r / 2 + q$ Load Indiance into Post-bac. $Z + r - 1, Bd_r - (2)_r / q)$ NomeLDS $Bd_r / r / q$ Load Diset from SBAM $Bd_r + (q)$ NomeST $X_r / Rr$ Store Indiance and Post-bac. $X + X + 1 / r / R$ NomeST $X_r / Rr$ Store Indiance and Post-bac. $Y + V + 1 / r / Rr$ NomeST $Y_r / Rr$ Store Indiance and Post-bac. $Y' - V - 1, (y) - Rr$ NomeST $Y_r / Rr$ Store Indiance and Post-bac. $Y' - V - 1, (y) - Rr$ NomeST $Y_r / Rr$ Store Indiance and Post-bac. $Y' - V - 1, (y) - Rr$ NomeST $Z_r / Rr$ Store Indiance and Post-bac. $Z' - Z + 1, (Z) - Rr$ NomeST $Z_r / Rr$ Store Indiance and Post-bac. $Z' - Z + 1, (Z) - Rr$ NomeST $Z_r / Rr$ Store Indiance and Post-bac. $Z' - Z + 1, (Z) - Rr$ NomeST $Z_r / Rr$ Store Indiance and Post-bac. $Z' - Z + 1, (Z) - Rr$ NomeST $Z_r / Rr$ Store Indiance and Post-bac. $Z' - Z + 1, (Z) - Rr$ NomeST $Z_r / Rr$ Store Indiance and Post-bac. $Z' - Z + 2 + 1$ Nom                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |               |             |                                  |                                             |         | 2       |

| LDRd $2$ Load Indirect and Post-Inc.Rd $-(2)$ NoneLDRd, ZLoad Indirect and Post-Inc.Rd $-(2)$ NoneLDRd, ZLoad Indirect and Post-Inc. $2 - 2 - 1$ , Rd $-(2)$ NoneLDSRd, LLoad Indirect with DoplacementRd $-(2, q)$ NoneSTX, RrStore IndirectD(2 - Rr, X + X + 1)NoneSTX, RrStore Indirect and Post-Inc.D(2 - Rr, X + X + 1)NoneST-X, RrStore Indirect and Post-Inc.D(2 - Rr, X + X + 1)NoneST-Y, RrStore Indirect and Post-Inc.D(2 - Rr, X + X + 1)NoneST-Y, RrStore Indirect and Post-Inc.D(Y - Rr, Y + Y + 1)NoneST-Y, RrStore Indirect and Post-Inc.D(Y - Rr, Y + Y + 1)NoneST-Y, RrStore Indirect and Post-Inc.D(Y - Rr, Y + Y + 1)NoneST-Y, RrStore Indirect and Post-Inc.D(Y - Rr, Y + Y + 1)NoneST-Z, RrStore Indirect and Post-Inc.D(Y - Rr, Y + Y + 1)NoneST-Z, RrStore Indirect and Post-Inc.D(Y - Rr, Y + Y + 1)NoneST-Z, RrStore Indirect and Post-Inc.D(Y - Rr, Y + Y + 1)NoneST-Z, RrStore Indirect and Post-Inc.D(Y - Rr, Y + Y + 1)NoneST-Z, RrStore Indirect and Post-Inc.D(Y - Rr, Y + Y + 1)NoneST-Z, RrStore Indirect and Post-Inc.D(Y - Rr, Y + Y + 1)NoneST-Z, Rr <t< td=""><td></td><td></td><td></td><td></td><td></td><td>2</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |               |             |                                  |                                             |         | 2       |

| LDBd $2 +$ Load Indirect and Pro-Boc. $Bd + (2), 2 - 2.1$ NoneLDDBd $2 + q_1$ Load Indirect with Displacement $Bd + (2), 2 - 2.1$ NoneLDSBd $k$ Load Direct with Displacement $Bd + - h)$ NoneSTX, RrStree Indirect and Pro-Boc. $(X) + Rr$ NoneSTX, RrStree Indirect and Pro-Boc. $(X) + Rr, X - X + 1 + 1$ NoneST-X, RrStree Indirect and Pro-Boc. $(Y) - Rr, Y - X + 1 + 1$ NoneST-Y, RrStree Indirect and Pro-Boc. $(Y) - Rr, Y - Y + 1$ NoneST-Y, RrStree Indirect and Pro-Boc. $(Y - Rr, Y - Y + 1)$ NoneST-Y, RrStree Indirect and Pro-Boc. $(Y - Rr, Y - Y + 1)$ NoneST-Y, RrStree Indirect and Pro-Boc. $(Y - Rr, Y - Y + 1)$ NoneST-Y, RrStree Indirect and Pro-Boc. $(Y - R, Y - Y + 1)$ NoneST-Y, RrStree Indirect and Pro-Boc. $(Y - R, Y - Y + 1)$ NoneST-Y, RrStree Indirect and Pro-Boc. $(Z - Rr, N - Z + Z + 1)$ NoneST-Z, RrStree Indirect and Pro-Boc. $(Z - Rr, N - Z + Z + 1)$ NoneST-Z, RrStree Indirect and Pro-Boc. $(Z - Rr, N - Z + Z + 1)$ NoneST-Z, RrStree Indirect and Pro-Boc. $(Z - Rr, N - Z + Z + 1)$ NoneST-Z, RrStore Indirect and Pro-Boc. $(Z - Rr, N - Z + Z + 1)$ NoneST-R, RrStore Indirect and Pro-Boc. $(Z - Rr, N - Z$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |               |             | •                                |                                             |         | 2       |

| LD         Rd. 2-q         Load Indirect and Pro-Duc.         2 - 2 - 1, 16 - (2),         None           LDD         Rd. 2-q         Load Direct from SRAM         Rd + (2 + q),         None           LDS         Rd, k         Load Direct from SRAM         Rd + (2 + q),         None           ST         X, Rr         Store Indirect and Pros-Duc.         (0) + Rr, X + X + 1         None           ST         X, Rr         Store Indirect and Pros-Duc.         X - X + 1, (1) + Rr         None           ST         Y, Rr         Store Indirect and Pros-Duc.         X - X + 1, (1) + Rr         None           ST         Y, Rr         Store Indirect and Pros-Duc.         Y - Y + 1, (1) + Rr         None           ST         Y, Rr         Store Indirect and Pros-Duc.         Y - Y + 1, (1) + Rr         None           ST         Y, Rr         Store Indirect and Pros-Duc.         Z - Z + 1, (2) + Rr         None           ST         Z, Rr         Store Indirect and Pros-Duc.         Z - Z + 1, (2) + Rr         None           ST         Z, Rr         Store Indirect and Pros-Duc.         Z - Z + 1, (2) + Rr         None           ST         Z, Rr         Store Indirect and Pros-Duc.         Z - Z + 1, (2) + Rr         None           ST         Z, Rr         <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |               |             |                                  |                                             |         | 2       |

| LDDR.d. 2r.q.Land Indirect with DisplacementRef $+(2+q)$ NoneLDSBd kLand Direct time SRAMRd $+(rb)$ NoneSTX, RrStore Indirect and Pac-Dac.(X) $+ R, X + X + 1$ NoneSTX, RrStore Indirect and Pac-Dac.X $+ X + 1, (X) + RrNoneSTY, RrStore Indirect and Pac-Dac.X + X + 1, (X) + RrNoneSTY, RrStore Indirect and Pac-Dac.(Y) + Rr, Y + Y + 1NoneSTY, RrStore Indirect and Pac-Dac.(Y) + Rr, Y - Y + 1NoneSTY, RrStore Indirect and Pac-Dac.(Y) + Rr, Y - Y + 1NoneSTY, RrStore Indirect and Pac-Dac.(Y) + Rr, Y - Y + 1NoneSTZ, RrStore Indirect and Pac-Dac.(Z) + Rr, Z - Z + 1NoneSTZ, RrStore Indirect and Pac-Dac.(Z) + Rr, Z - Z + 1NoneSTZ, RrStore Indirect and Pac-Dac.(Z) + Rr, Z - Z + 1NoneSTZ, RrStore Indirect and Pac-Dac.(Z) + Rr, Z - Z + 1NoneSTZ, RrStore Indirect and Pac-Dac.(Z) + Rr, Z - Z + 1NoneSTZ, RrStore Indirect and Pac-Dac.(Z) + Rr, Z - Z + 1NoneSTZ, RrStore Indirect and Pac-Dac.(Z) + Rr, Z - Z + 1NoneSTZ, RrStore Indirect and Pac-Dac.(Z) + Rr, Z - Z + 2NoneSTZ, RrStore Indirect and Pac-Dac.(Z) + Rr, Z - Z + 2NoneSTSto$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |               |             |                                  |                                             |         | 2       |

| LDS         R4, k         Load Direct from SRAM         R4 + (b)         None           ST         X, Rr         Store Indirect and Post-Inc.         (b) + Rr, X + X + 1         None           ST         -X, Rr         Store Indirect and Post-Inc.         (b) + Rr, X + X + 1         None           ST         -X, Rr         Store Indirect and Post-Inc.         (b) + Rr, Y + Y + 1         None           ST         Y, Rr         Store Indirect and Post-Inc.         (Y) + Rr, Y + Y + 1         None           ST         Y, Rr         Store Indirect and Post-Inc.         (Y) + Rr, Y + Y + 1         None           ST         Y, Rr         Store Indirect and Post-Inc.         (Y) + Rr, Y + Y + 1         None           ST         Y, Rr         Store Indirect with Displacement         (Z) + Rr         None           ST         Z, Rr         Store Indirect and Post-Inc.         (Z) + Rr         None           ST         Z, Rr         Store Indirect and Post-Inc.         (Z) + Rr         None           ST         Z, Rr         Store Indirect and Post-Inc.         (Z) + Rr         None           ST         Z, Rr         Store Indirect and Post-Inc.         (Z) + Rr         None           ST         Z, Rr         Store Indinord         Rd + Infor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |               |             |                                  |                                             |         | 2       |