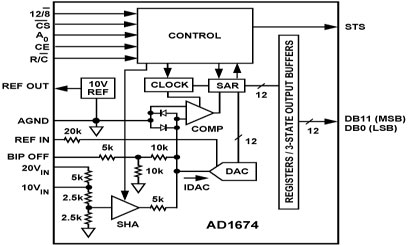

图1所示为AD1674的内部结构框图,图2所示为其引脚排列。

AD1674的引脚按功能可分为逻辑控制端口、并行数据输出端口、模拟信号输入端口和电源端口四种类型。

(1)逻辑控制端口

12/8:数据输出位选择输入端。当该端输入为低时,数据输出为双8位字节;当该端输入为高时,数据输出为单12位字节。

CS:片选信号输入端;

R/C:读/转换状态输入端。在完全控制模式下,输入为高时为读状态;输入为低时为转换状态;在独立工作模式下,在输入信号的下降沿时开始转换。

CE:操作使能端;输入为高时,芯片开始进行读/转换操作。

A0:位寻址/短周期转换选择输入端。在转换开始时,若A0为低,则进行12位数据转换;若A0为高,则进行周期更短的8位数据转换;当R/C=1且12/8=0时,若A0为低,则在高8位(DB4~DB11)作数据输出;若A0为高,则在DB0~DB3和DB8~DB11作数据输出,而DB4~DB7置零。

STS:转换状态输出端。输出为高时表明转换正在进行;输出为低时表明转换结束。

(2)并行数据输出端口

DB11~DB8:在12位输出格式下,输出数据的高4位;在8位输出格式下,A0为低时也可输出数据的高4位。

(3)模拟信号输入端口

10VIN:10V范围输入端,包括0V~10V单极输入或±5V双极输入;

20VIN:20V范围输入端,包括0V~20V单极输入或±10V双极输入;

应当注意的是:如果已选择了其中一种作为输入范围,则另一种不得再连接合作。

(4)供电电源端口

REF IN:基准电压输入端,在10V基准电源上接50Ω电阻后连于此端;

REF OUT:+10V基准电压输出端;

BIP OFF:双极电压偏移量调整端,该端在双极输入时可通过50Ω电阻与REF

OUT端相连;在单极输入时接模拟地。图3给出了AD1674在单极和双极输入时的两种连接电路。

VCC:+12V/+15V模拟供电输入;

VEE:-12V/-15V模拟供电输入;

VLOGIC:+5V逻辑供电输入;

AGND/DGND:模拟/数字接地端;

表1给出了AD1674的逻辑控制真值表。

表1 AD1674控制逻辑真值表

| CE |

CS |

R/C |

12/8 |

A0 |

执 行 操 作 |

| 0 |

× |

× |

× |

× |

无操作 |

| × |

1 |

× |

× |

× |

无操作 |

| 1 |

0 |

0 |

× |

0 |

启动12位数据转换 |

| 1 |

0 |

0 |

× |

1 |

启动8位数据转换 |

| 1 |

0 |

1 |

1 |

× |

允许12位并行输出 |

| 1 |

0 |

1 |

1 |

0 |

允许高8位并行输出 |

| 1 |

0 |

1 |

0 |

1 |

允许低4位并行输出 |

工作时序

AD1674的工作模式可分为全控(Full-Con-trol)模式和独立(Stand-Alone)模式,而在这两种模式下,这的工作时序是同的。独立模式主要用于具有专门输入端系统,因而不需要有全总线的接口能力。而采用全控工作模式则有利于和CPU进行总线连接。

图4、图5分别是AD1674在全控工作模式下的转换启动时序和读操作时序。转换启动时,在CE和CS有效之前,R/C必须为低,如果R/C为高,则立即进行读操作,这样会造成系统总线的冲突。一旦转换开始,STS立即为高,系统将不再执行转换开始命令,直到这次转换周期结束。而数据输出缓冲器将比STS提前0.6μs变低,且在整个转换期间内不导通。

4 应用电路

图6为某新型国产机载武器系统的数据采集处理部分的电路原理框图。来自保传感器的十六路模拟信号经过多路开关切换后送至高精密运放进行缓冲放大,同时还要保持信号的采样精度。AD1674T被接在±10V双极模拟电压输入模式,使用的是内部基准源和时钟。从开关选通模拟信号到A/D转换以及数据输出均由ADSP2100微处理器进行逻辑控制,每个这样的变换周期均为64μs,因而完成16个通道的模拟转换大约需要1ms的时间,可以符合该系统的响应技术要求。